#### DESIGN AND CONTROL OF A BATTERY CHARGER FOR ELECTRIC VEHICLES

#### **Adrià Marcos Pastor**

**ADVERTIMENT.** L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

## Adrià Marcos Pastor

# DESIGN AND CONTROL OF A BATTERY CHARGER FOR ELECTRIC VEHICLES

## DOCTORAL THESIS

Departament d'Enginyeria Electrònica, Elèctrica i Automàtica

Universitat Rovira i Virgili

## Adrià Marcos Pastor

# DESIGN AND CONTROL OF A BATTERY CHARGER FOR ELECTRIC VEHICLES

DOCTORAL THESIS

Supervised by Dr. Enric Vidal Idiarte

and Dr. Àngel Cid Pastor

Departament d'Enginyeria Electrònica, Elèctrica i Automàtica

Universitat Rovira i Virgili

Tarragona, 2015

Departament d'Enginyeria Electrònica,

Elèctrica i Automàtica

Avinguda Països Catalans, 26

43007 Tarragona

Tel. +34 977 55 96 10

Fax +34 977 55 96 05

WE STATE that the present study, entitled "Design and control of a battery charger for electric vehicles", presented by Adrià Marcos Pastor for the award of the degree of Doctor, has been carried out under our supervision at the Department of Electronic, Electric and Automatic Control Engineering of this university.

Tarragona, 31<sup>th</sup> August 2015

Doctoral Thesis Supervisor

Doctoral Thesis Supervisor

Dr. Enric Vidal Idiarte

Dr. Angel Cid Pastor

> Per a aquells que han estat, els que som, í els que han de venír.

En primer lloc, voldria agrair als meus directors de tesis, el Dr. Enric Vidal Idiarte i el Dr. Àngel Cid Pastor, l'oportunitat que m'han donat de treballar en el desenvolupament d'aquesta tesi dins el Grup de recerca en Automàtica i Electrònica Industrial (GAEI) de la Universitat Rovira i Virgili. Els agraeixo profundament les hores que m'han dedicat i tot el suport que m'han donat al llarg d'aquest temps.

Voldria agrair a tots els membres del laboratori del GAEI que he tingut la sort de conèixer durant aquest període les hores de treball compartides: Dr. J. M. Bosque, Dr. F. Flores-Bahamonde, Dra. S. Mendez, Dr. H. Ramirez, Dr. M. Bodetto, Dr. G. Ruiz, R. Bonache, P. Gaona, T. Martinez, O. Avinyo, R. Marcos, X. Alsina, J. I. Talpone, J. M. Salmeron, A. Teixido, S. Wu-Fu i, en especial, als meus companys de despatx, la Dra. L. Albiol-Tendillo i el Dr. A. Leon-Masich. Agrair la col·laboració dels diferents estudiants que han participat en la implementació de prototips en el marc del seus respectius projectes finals de carrera: F. Mena, M. Margalef, J. Perello, E. Zahino i A. Favian.

Agrair també la proximitat dels professors del departament, en especial, el Dr. A. El Aroudi, el Dr. J. Calvente i el Prof. L. Martinez Salamero per la seva col·laboració en diferents publicacions.

Special thanks to Prof. M. Milanovič for giving me the opportunity to come to the Faculty of Electrical Engineering and Computer Science FERI of the University of Maribor and receiving me like another member of the team. Special thanks also to Dr. T. Konjedic, L. Korošec, Dr. M. Truntič and Dr. M. Rodic for their valuable assistance and making my stay one of my best experiences of my life.

Finalment, agrair a la meva família la fe que sempre han tingut en mi. En especial als meus pares Ester i Aureli, i al meu germà Guillem, per ensenyar-me el valor de l'esforç i pel seu suport incondicional. Al meu avi, César Pastor, per la seva col·laboració en la meva formació i haver esperat amb il·lusió veure'm arribar fins aquí. Als altres avis, Manolita Bertrán, Aureli Marcos i Carmen Teigeiro, que tot i ja no ser-hi, també m'han ajudat a créixer personalment. A Cristina Vives, per ser la meva companya de viatge, per la seva comprensió i ajudar-me en tot moment. A Sílvia Vives per la seva contribució en la revisió de la tesi. I als amics, aquells que per molt anys que passin, no canviaran mai.

This work was supported by the Spanish Ministerio de Economía y Competitividad under Grant BES-2011-045309 and by the Spanish Ministerio de Educación e Innovación under Projects DPI2010-16084, DPI2013-47437-R, DPI2013-47293-R and CSD2009-00046.

### **Contents**

| L | ist of f | īgures                                                 | XV    |

|---|----------|--------------------------------------------------------|-------|

| L | ist of t | ables                                                  | xxiii |

| L | ist of a | abbreviations, symbols and variables                   | XXV   |

| A | bstrac   | rt                                                     | xxix  |

| 1 | Int      | roduction                                              | 1     |

|   | 1.1      | Battery charging modes for EVs                         | 3     |

|   | 1.2      | EVs battery chargers                                   | 4     |

|   | 1.3      | EVs battery chargers architectures                     | 4     |

|   | 1.3.     | .1 PFC stage circuit topologies                        | 5     |

|   | 1.3.     | .2 Battery current regulation stage circuit topologies | 7     |

|   | 1.4      | Battery charger controllers                            | 10    |

|   | 1.5      | Research objectives and methodology                    | 15    |

| 2 | Bat      | ttery charger circuit design                           | 17    |

|   | 2.1      | Battery charger overview                               | 17    |

|   | 2.1.     | .1 Proposed topology                                   | 17    |

|   | 2.1.     | .2 Design Specifications                               | 18    |

|   | 2.1.     | .3 Interleaving technique                              | 19    |

|   | 2.1.     | .4 Converters' bidirectional capability                | 24    |

|   | 2.1.     | .5 Control stage structure                             | 26    |

|   | 2.2      | Design of the power factor correction stage            | 27    |

|   | 2.2.     | .1 PFC inductor design                                 | 27    |

|   | 2.2.     | .2 DC-link capacitor design                            | 29    |

|   | 2.2. | .3     | PFC power switches design                   | . 30 |

|---|------|--------|---------------------------------------------|------|

|   | 2.2. | .4     | PFC sensing circuitry                       | . 31 |

|   | 2.3  | Des    | ign of the battery current regulation stage | . 32 |

|   | 2.3. | .1     | BCR inductor design                         | . 34 |

|   | 2.3. | .2     | Output capacitor design.                    | . 35 |

|   | 2.3. | .3     | BCR power switches design                   | . 35 |

|   | 2.3. | .4     | BCR sensing circuitry                       | . 36 |

|   | 2.4  | Des    | ign of the grid-synchronised rectifier      | . 36 |

|   | 2.4. | .1     | Power switches                              | . 36 |

|   | 2.4. | .2     | Input capacitor design                      | . 37 |

|   | 2.5  | Des    | ign of the control stage                    | . 38 |

|   | 2.5. | .1     | Sensing signals conditioning                | . 38 |

|   | 2.5. | .2     | Digital Signal Controller                   | . 40 |

|   | 2.5. | .3     | Control signals logic circuit               | . 41 |

|   | 2.6  | Sun    | nmary                                       | . 42 |

| 3 | Bat  | tery   | charger modelling                           | . 43 |

|   | 3.1  | Stea   | ndy-state averaged model                    | . 43 |

|   | 3.2  | Pow    | ver converters modelling                    | . 45 |

|   | 3.2. | .1     | Continuous-time modelling                   | . 45 |

|   | 3.2. | .2     | Discrete-time modelling                     | . 50 |

|   | 3.2. | .3     | Summary                                     | . 53 |

|   | 3.3  | Con    | clusions                                    | . 53 |

| 4 | Dig  | ital c | ontroller design                            | . 55 |

|   | 4.1  | Dig    | ital controller overview                    | . 55 |

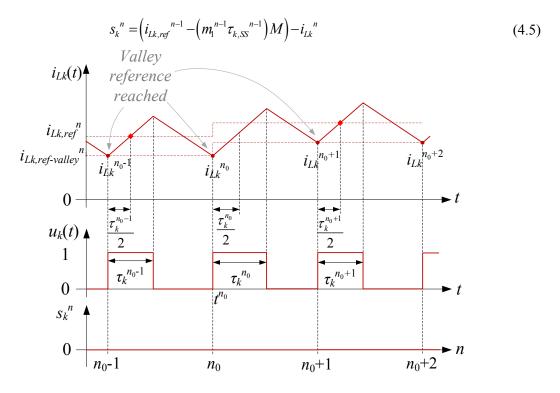

|   | 4.2 | Discrete-time SM-based inductor current-mode controllers              | 59  |

|---|-----|-----------------------------------------------------------------------|-----|

|   | 4.2 | 1 Discrete-time sliding control surface                               | 59  |

|   | 4.2 | 2 Equivalent control                                                  | 61  |

|   | 4.2 | 3 Ideal discrete-time dynamics                                        | 62  |

|   | 4.2 | 4 Equilibrium point                                                   | 65  |

|   | 4.2 | 5 Stability analysis of the equilibrium point                         | 66  |

|   | 4.3 | Design of the DC-link voltage regulation loop                         | 69  |

|   | 4.4 | Battery voltage controller design                                     | 76  |

|   | 4.5 | Sequential execution of the control algorithm                         | 77  |

|   | 4.6 | Conclusions                                                           | 81  |

| 5 | Sin | nulation and experimental results                                     | 83  |

|   | 5.1 | PSIM simulation model                                                 | 83  |

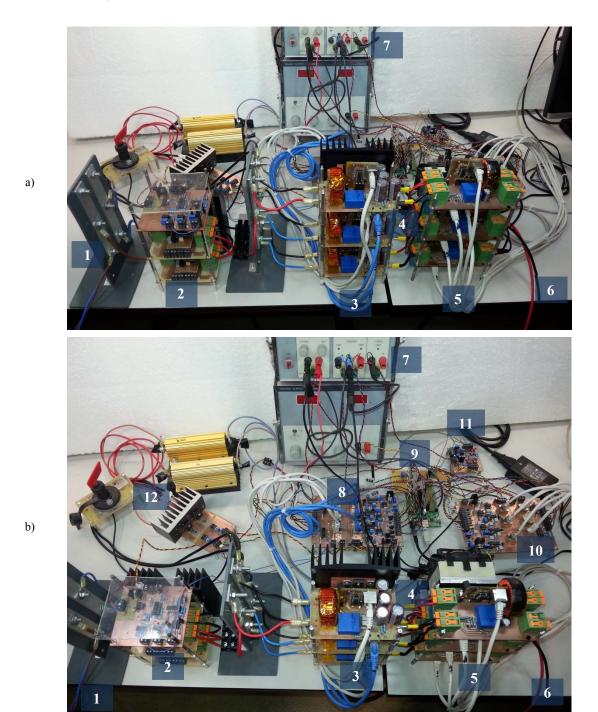

|   | 5.2 | Experimental set-up.                                                  | 88  |

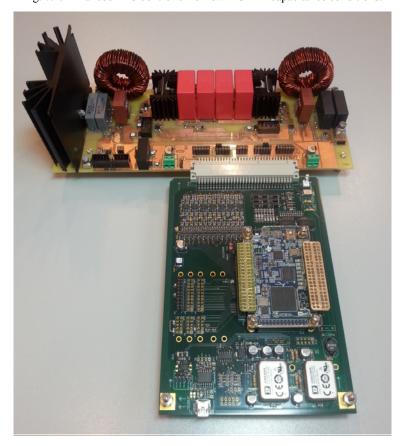

|   | 5.2 | 1 Implemented prototype                                               | 88  |

|   | 5.2 | 2 Laboratory equipment                                                | 89  |

|   | 5.3 | Grid-to-Vehicle operation                                             | 90  |

|   | 5.4 | Vehicle-to-Grid operation                                             | 95  |

|   | 5.5 | Conclusions and future work                                           | 97  |

| 6 | DC  | -link capacitance reduction                                           | 99  |

|   | 6.1 | Problem statement                                                     | 99  |

|   | 6.2 | Conventional design of the DC-link capacitor                          | 101 |

|   | 6.3 | Design of a reduced DC-link capacitor to supply a constant power load | 105 |

|   | 6.3 | 1 Minimum DC-link capacitor design                                    | 106 |

|   | 6.3 | 2 Constant vs variable switching frequency PFC controllers            | 110 |

| R | eference | 25                                                                           | . 151 |

|---|----------|------------------------------------------------------------------------------|-------|

| C | ontribu  | tions                                                                        | . 149 |

| 7 | Conc     | clusions and future work                                                     | . 145 |

|   | 6.5      | Conclusions and future work                                                  | . 142 |

|   | 6.4      | DC-link voltage regulation from the second stage                             | . 135 |

|   | 6.3.7    | Simulation and experimental results                                          | . 130 |

|   | 6.3.6    | Analogue controller implementation                                           | . 126 |

|   | 6.3.5    | DC-link voltage controller design based on Middlebrook's stability criterion | . 119 |

|   | 6.3.4    | Small-signal modelling                                                       | . 116 |

|   | 6.3.3    | Sliding-mode control application                                             | . 113 |

# List of figures

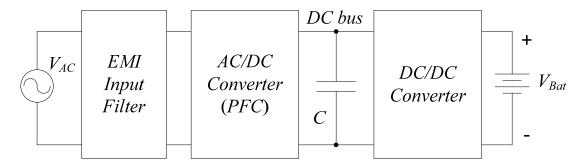

| Fig. | 1.1. General block diagram of a single-phase on-board battery charger                                                                                                                                                                                                                                                | 5    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

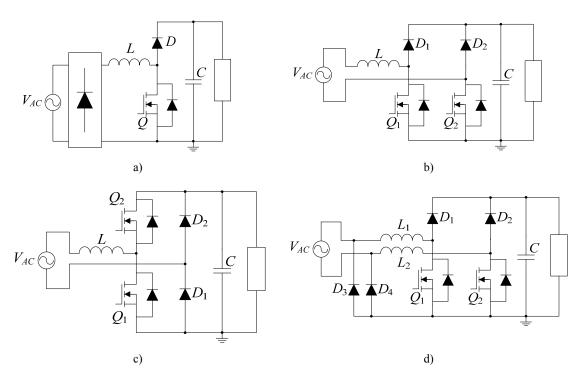

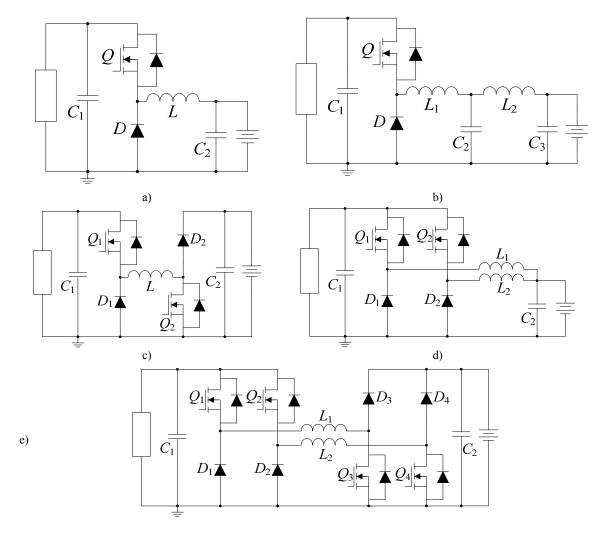

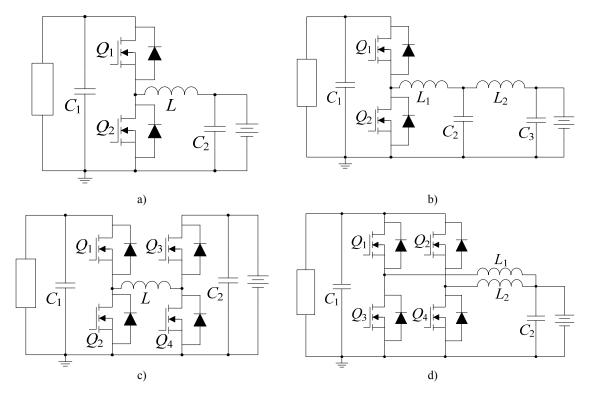

| Fig. | 1.2. Unidirectional boost-based AC/DC converters. a) Diode rectifier and boost converter. Bridgeless topologies b) Basic topology [39]. c) Totem-pole [40]. d) Dual-boost or semi-bridgeless [41].                                                                                                                   | 5    |

| Fig. | 1.3. Unidirectional interleaved boost-based AC/DC converters. a) Basic interleaved [43, 44]. b) Totem-pole interleaved [47]. c) Bridgeless interleaved [46]                                                                                                                                                          | 6    |

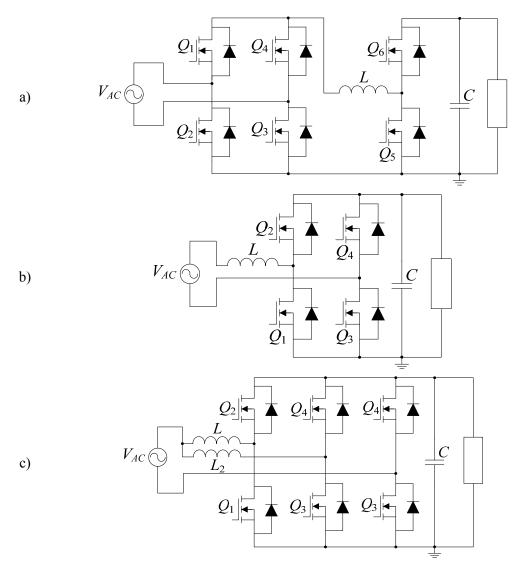

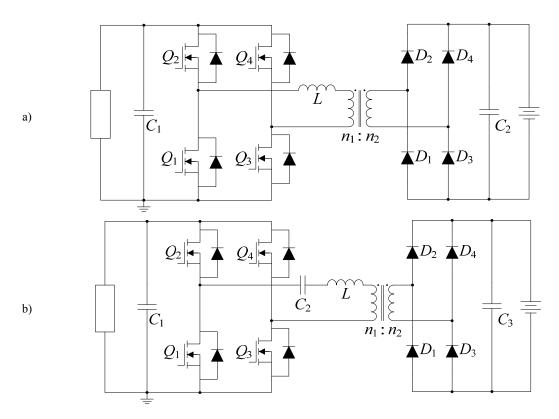

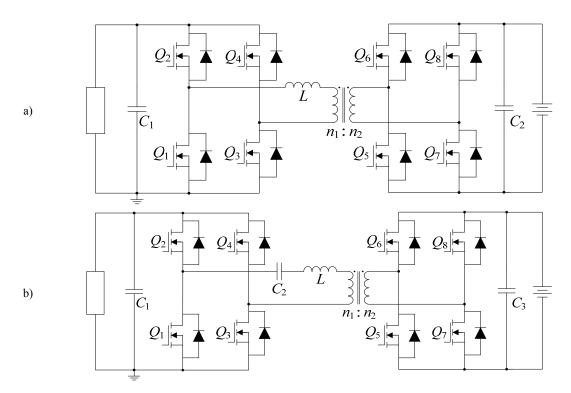

| Fig. | 1.4. Bidirectional boost-based AC/DC converters. a) Boost converter with synchronous rectifier. b) Full-bridge boost rectifier [48]. c) Full-bridge interleaved [48, 49].                                                                                                                                            | 7    |

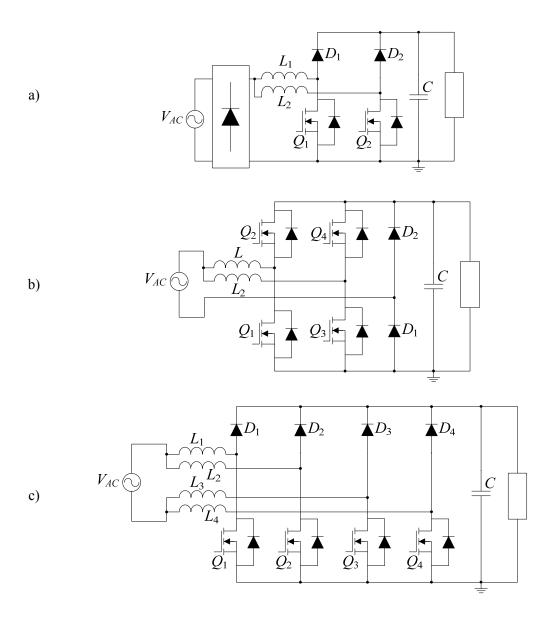

| Fig. | 1.5. Unidirectional non-isolated DC/DC converters. a) Buck. b) Buck with output filter. c) Buck-boost. d) Interleaved buck [50]. e) Interleaved buck-boost [51]                                                                                                                                                      | 8    |

| Fig. | 1.6. Unidirectional isolated DC/DC converters. a) Phase-shifted full-bridge [53]. b) Full-bridge series resonant [54]                                                                                                                                                                                                | 9    |

| Fig. | 1.7. Bidirectional non-isolated DC/DC converters. a) Two quadrant buck [55]. b) Two quadrant buck with output filter [59]. c) Buck-boost [55]. d) Interleaved two quadrant buck [58].                                                                                                                                | 9    |

| Fig. | 1.8. Bidirectional isolated DC/DC converters. a) Dual-active bridge [53]. b) Full-bridge series resonant [61].                                                                                                                                                                                                       | 10   |

| Fig. | 1.9. Block diagram of a generic battery charger controllers.                                                                                                                                                                                                                                                         | 11   |

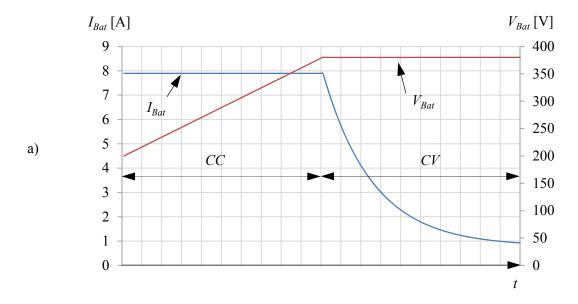

| Fig. | 1.10. CC-CV battery charging profile.                                                                                                                                                                                                                                                                                | 12   |

| Fig. | 1.11. Loss-free resistor (LFR) model.                                                                                                                                                                                                                                                                                | 13   |

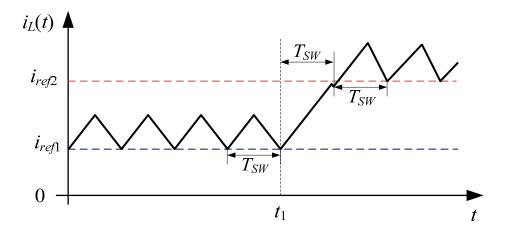

| Fig. | 1.12. Response of an inductor current in front of a reference step change in case of using a hysteretic current controller. $T_{SW1}$ and $T_{SW2}$ are the switching periods for the equilibrium points corresponding to $i_{ref1}$ and $i_{ref2}$ respectively and $H$ represents the value of a hysteresis bound. | . 14 |

| Fig. | 1.13. Response of an inductor current in front of a reference step change in case of using the proposed controller. $T_{SW}$ is the constant switching period                                                                                                                                                        | 14   |

| Fig. | 1.14. Simplified block diagram of the battery charger control algorithm                                                                                                                                                                                                           | . 15 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

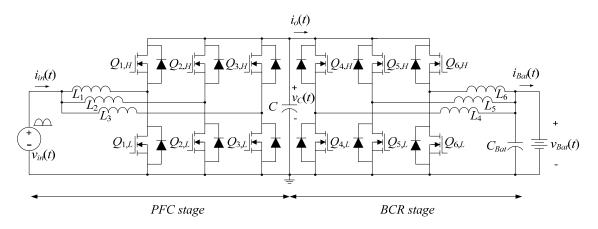

| Fig. | 2.1. Proposed battery charger topology.                                                                                                                                                                                                                                           | . 18 |

| Fig. | 2.2. Parallel connection of the PFC bidirectional boost converters.                                                                                                                                                                                                               | . 20 |

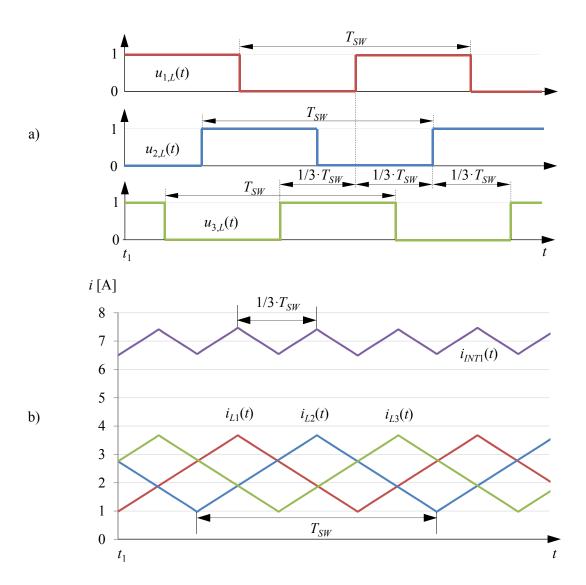

| Fig. | 2.3.Interleaved waveforms of the PFC stage. a) Phase-shifted control signals. b) Inductor currents $i_{Lj}(t)$ and total current $i_{INT1}(t)$                                                                                                                                    | . 21 |

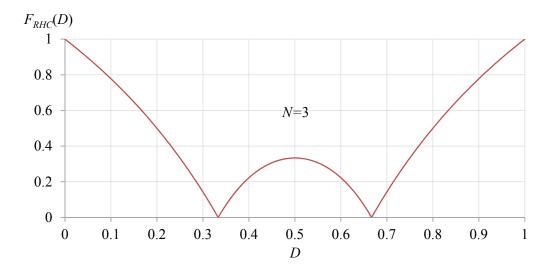

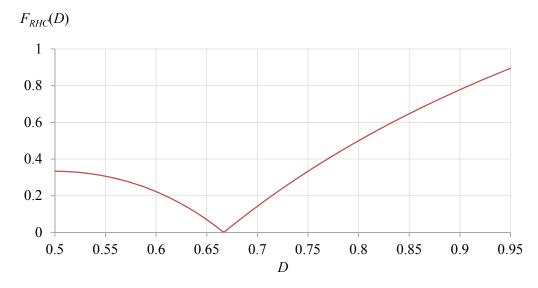

| Fig. | 2.4. Ripple harmonic cancellation function $F_{RHC}(D)$ for three interleaved cells                                                                                                                                                                                               | . 22 |

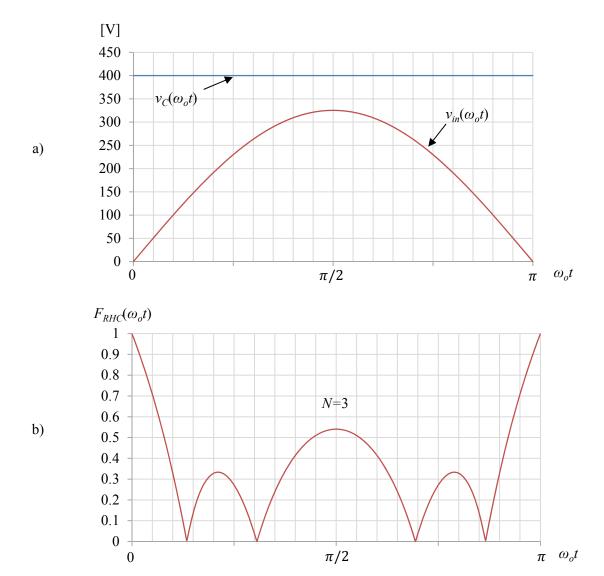

| Fig. | 2.5. PFC stage case for high line voltage conditions (230 $V_{RMS}$ ). a) Theoretical rectified input voltage and DC-link voltage over one half-line cycle. b) Resulting ripple harmonic cancellation function over one half-line cycle.                                          | . 22 |

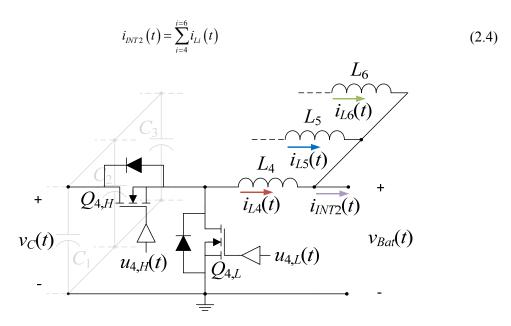

| Fig. | 2.6. Parallel connection of the bidirectional buck converters of the BCR stage                                                                                                                                                                                                    | . 23 |

| Fig. | 2.7. Parallel connection of the bidirectional buck converters of the BCR stage                                                                                                                                                                                                    | . 23 |

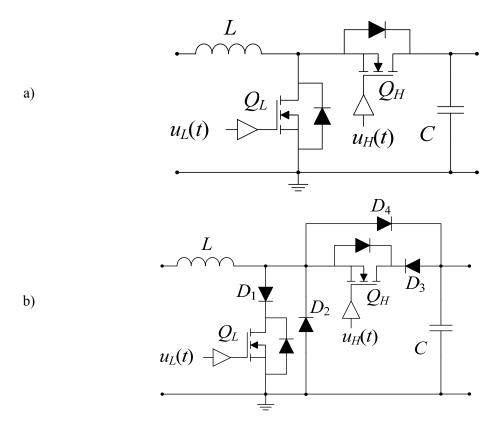

| Fig. | 2.8. Bidirectional boost converter. a) Using two synchronous MOSFETs. b) Adopted alternative.                                                                                                                                                                                     | . 24 |

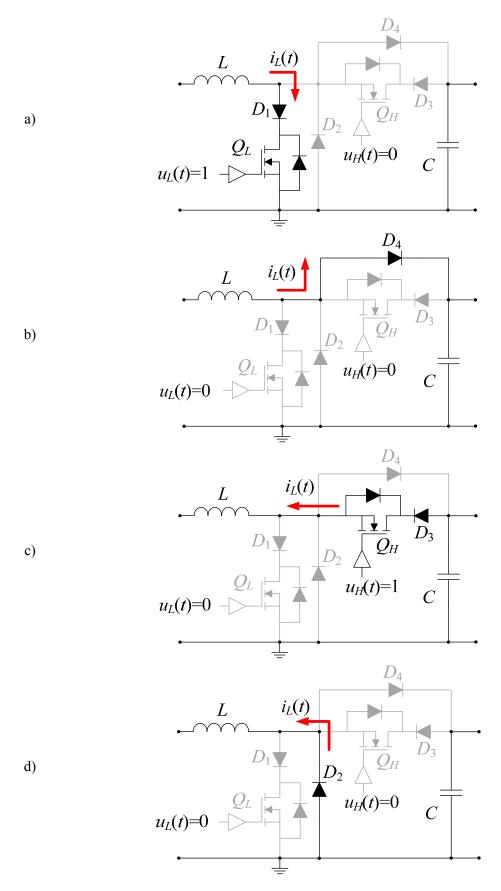

| Fig. | 2.9. Converters' asynchronous operation with the adopted alternative exemplified in a boost converter. Stepping up mode. a) On state. b) Off state. Stepping down mode. c) ON-state. d) OFF-state.                                                                                | . 25 |

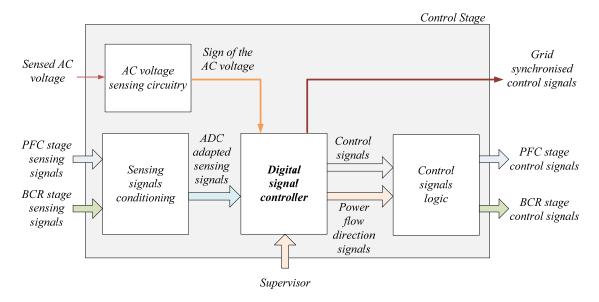

| Fig. | 2.10. General structure of the control stage.                                                                                                                                                                                                                                     | . 26 |

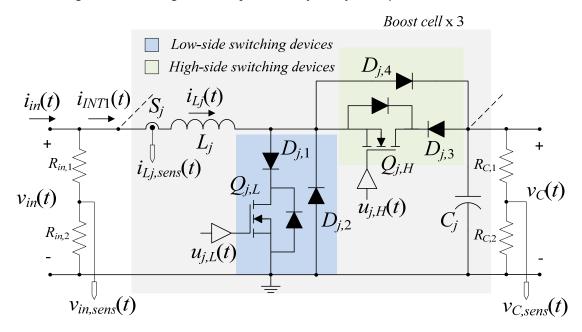

| Fig. | 2.11. Bidirectional boost/buck cell of the PFC stage.                                                                                                                                                                                                                             | . 27 |

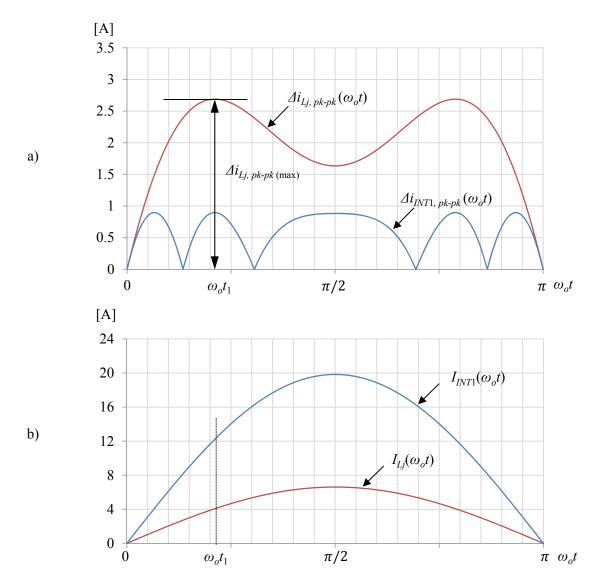

| Fig. | 2.12. Graphic comparison over half line cycle between a) peak-to-peak current ripple amplitudes $\Delta i_{Lj,pk-pk}(\omega_o t)$ and $\Delta i_{INT1,pk-pk}(\omega_o t)$ , b) local average currents $I_{Lj}(\omega_o t)$ and $I_{INT1}(\omega_o t)$ under full load conditions. | . 29 |

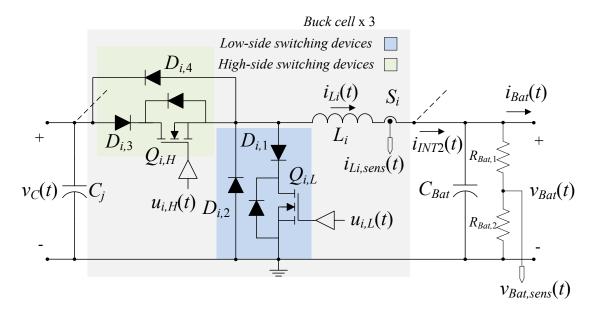

| Fig. | 2.13. Bidirectional buck cell of the BCR stage.                                                                                                                                                                                                                                   | . 32 |

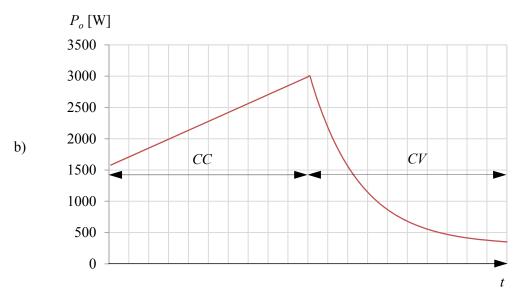

| Fig. | 2.14. Battery charging profile vs time. a) Battery current and voltage. b) Power delivered to the battery                                                                                                                                                                         | . 33 |

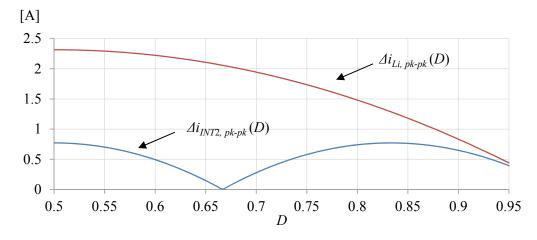

| Fig. | 2.15. Graphic comparison of peak-to-peak current ripple amplitudes $\Delta i_{Li,pk-pk}(D)$ and                                                                                                                                                                                   | 2    |

|      | $\Delta i_{INT2,pk-pk}(D)$ for the operative range of the BCR stage                                                                                                                                                                                                               | . 34 |

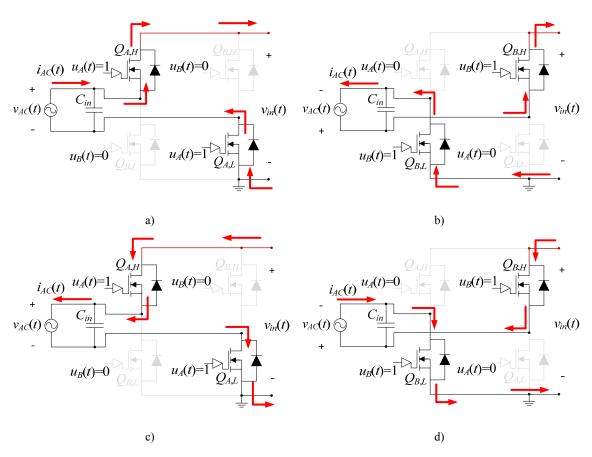

| Fig. 2.16. Bidirectional operation of the full-bridge grid-synchronised rectifier: $u_A(t)=1$ and                                                                                                          |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $u_B(t)=0$ when $v_{AC}(t)>0$ , $u_A(t)=0$ and $u_B(t)=1$ when $v_{AC}(t)<0$ . G2V operation a) $v_{AC}(t)>0$ ,                                                                                            |    |

| b) $v_{AC}(t) < 0$ . V2G operation a) $v_{AC}(t) > 0$ , b) $v_{AC}(t) < 0$                                                                                                                                 | 37 |

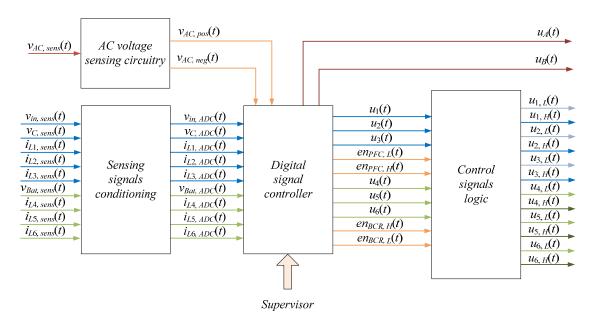

| Fig. 2.17. Complete signal connection diagram of the control stage.                                                                                                                                        | 38 |

| Fig. 2.18. Simplified scheme of the sensing signals conditioning block.                                                                                                                                    | 39 |

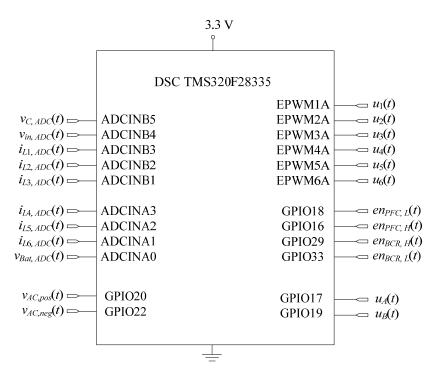

| Fig. 2.19. Pin out connection of the DSC.                                                                                                                                                                  | 40 |

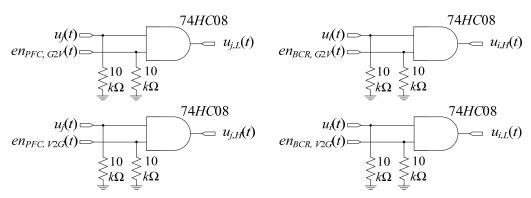

| Fig. 2.20. Simplified scheme of the control signals logic block.                                                                                                                                           | 41 |

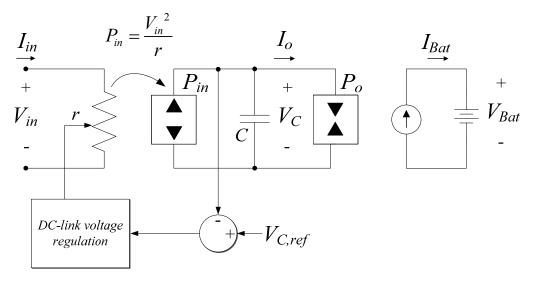

| Fig. 3.1. General view of the two-cascaded stages of the battery charger.                                                                                                                                  | 43 |

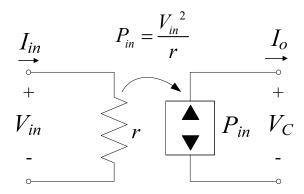

| Fig. 3.2. LFR model.                                                                                                                                                                                       | 44 |

| Fig. 3.3. Proportionality between input current $I_{in}$ and input voltage $V_{in}$                                                                                                                        | 44 |

| Fig. 3.4. Equivalent representation of the PFC stage based on three parallel connected LFRs.                                                                                                               | 45 |

| Fig. 3.5. Continuous-time modelling of the PFC stage cells. Boost converter connected to a a) CPL for G2V operation mode, b) CPS for V2G operation mode                                                    | 46 |

| Fig. 3.6. Continuous-time modelling of the BCR stage cells. Buck converter connected to a b) Thévenin's simplified model of a battery, c) a resistive load, d) a DC voltage source for V2G operation mode. | 46 |

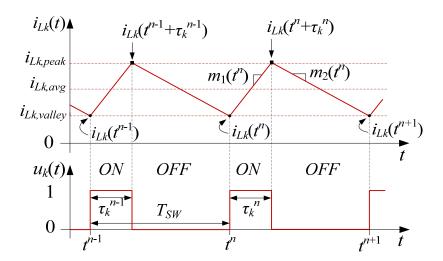

| Fig. 3.7. Theoretical behaviour of one cell inductor current.                                                                                                                                              | 47 |

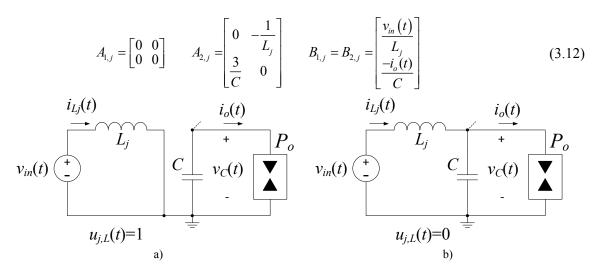

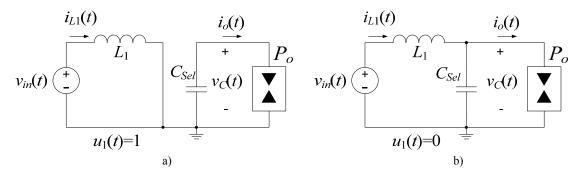

| Fig. 3.8. Ideal boost converter conduction topologies. a) On-state for $u_{j,L}(t)=1$ . b) Off-state for $u_{j,L}(t)=0$ .                                                                                  | 48 |

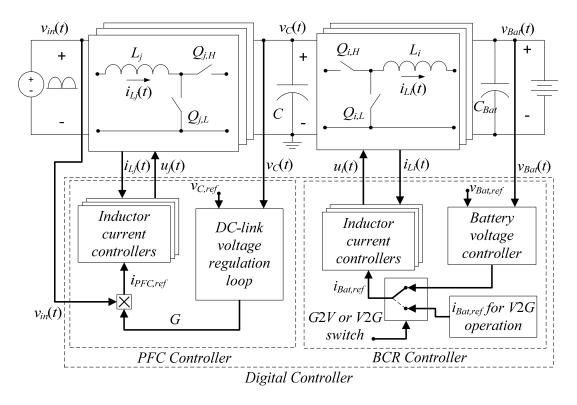

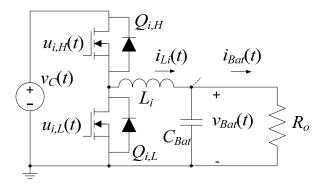

| Fig. 3.9. Ideal buck converter conduction topologies during G2V operation. a) On-state for $u_{i,H}(t)=1$ , b) Off-state for $u_{i,H}(t)=0$ .                                                              | 49 |

| Fig. 3.10. Ideal buck converter conduction topologies during V2G operation. a) On-state for $u_{i,H}(t)=1$ , b) Off-state for $u_{i,H}(t)=0$ .                                                             | 49 |

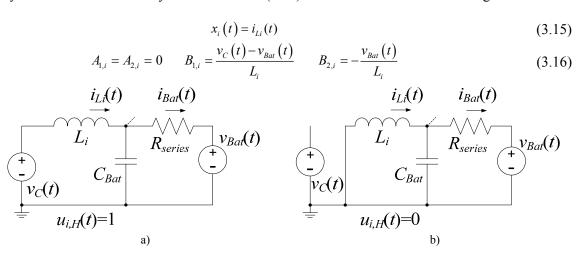

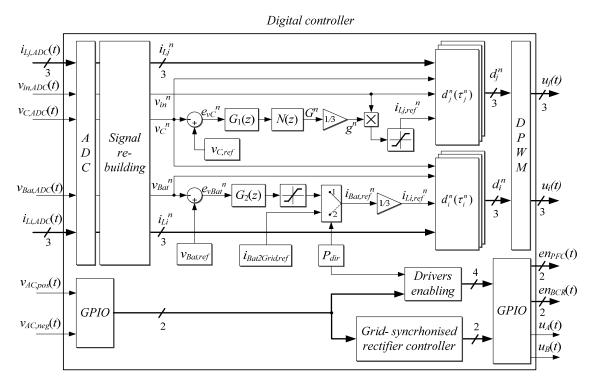

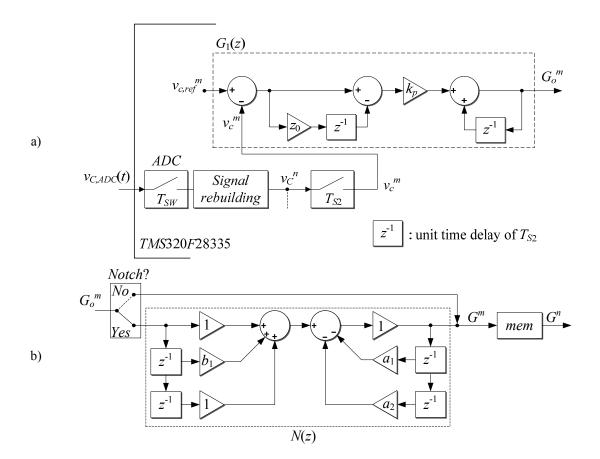

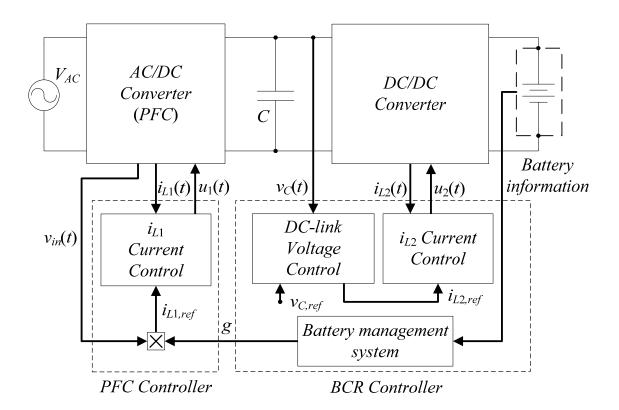

| Fig. 4.1. Simplified overview of both digitally controlled stages of the battery charger                                                                                                                   | 56 |

| Fig. 4.2. Block diagram of the digital controller.                                                                                                                                                         | 58 |

| Fig. 4.3. Different types of current-mode control techniques. a) Valley, b) average and c)                                                                                                                 |    |

| neak                                                                                                                                                                                                       | 59 |

| _      | 4.4. Response example of the discrete-time SM-based current-mode controller in average mode.                                                          | 60 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | 4.5. Buck converter cell of the BCR stage cell with a resistive load that models the pattery.                                                         | 65 |

| Fig. 4 | .6. Large-signal averaged system's modelling.                                                                                                         | 68 |

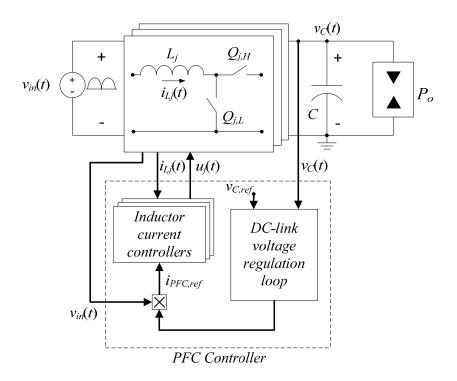

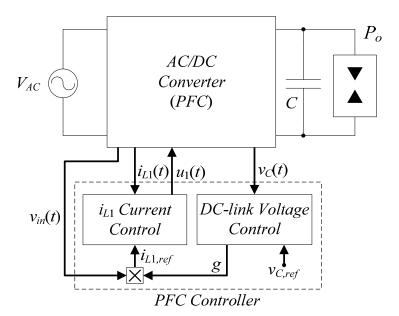

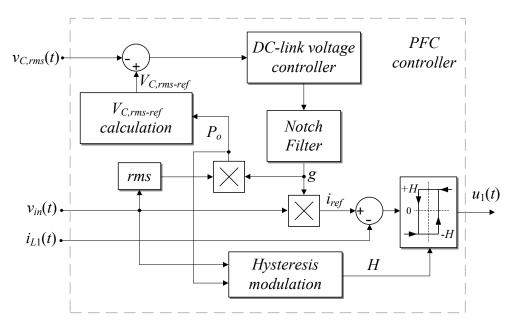

| Fig. 4 | .7. PFC controller stage of the battery charger.                                                                                                      | 70 |

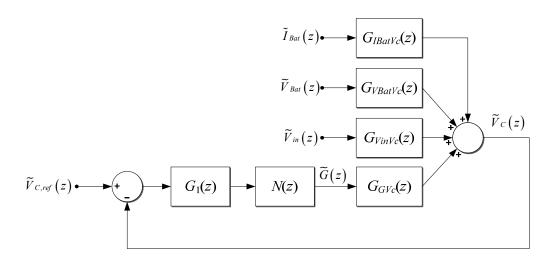

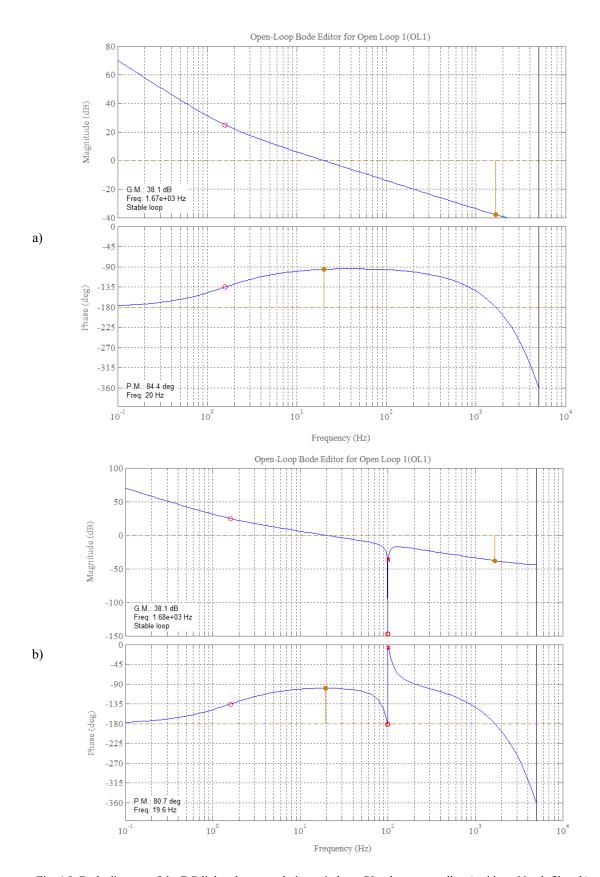

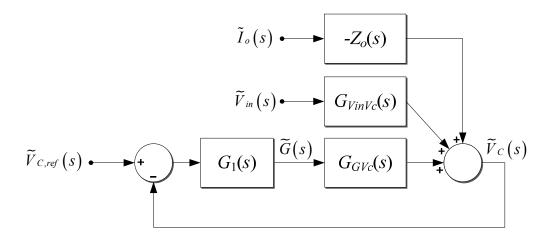

| _      | 8.8. Small-signal model of the DC-link voltage with sliding-mode current control and outer voltage control loop.                                      | 71 |

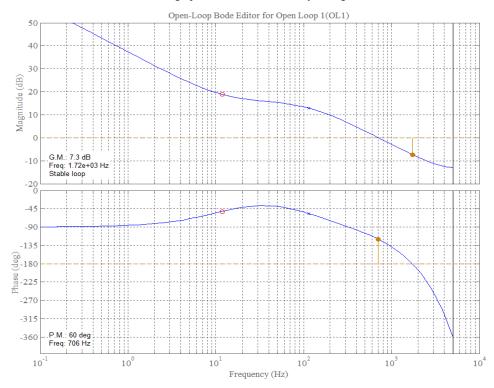

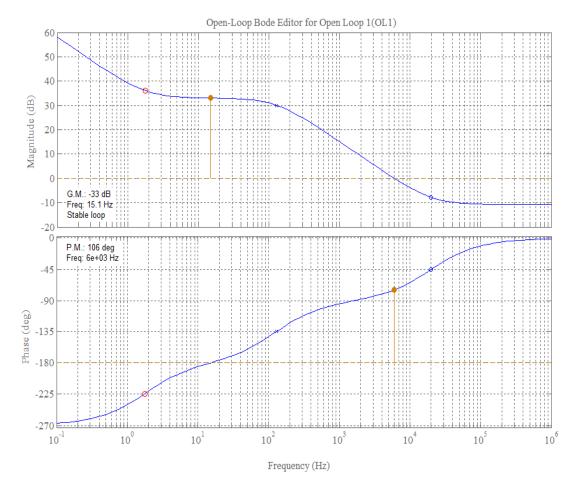

| -      | .9. Bode diagram of the DC-link voltage regulation gain loop. PI voltage controller a) without Notch filter, b) with Notch filter.                    | 75 |

| Fig. 4 | .10. Block diagram implementation of a) $G_1(z)$ , b) $N(z)$                                                                                          | 76 |

| Fig. 4 | .11. Magnitude and phase of the battery voltage regulation gain loop.                                                                                 | 77 |

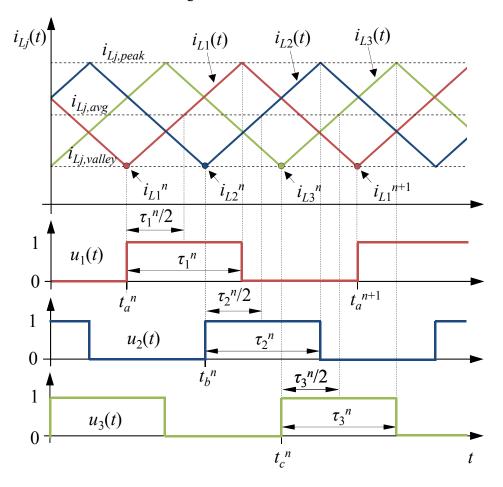

| _      | 1.12. Interleaving operation example. Interleaved inductor currents $i_{Lj}(t)$ and control signals $u_j(t)$ .                                        | 78 |

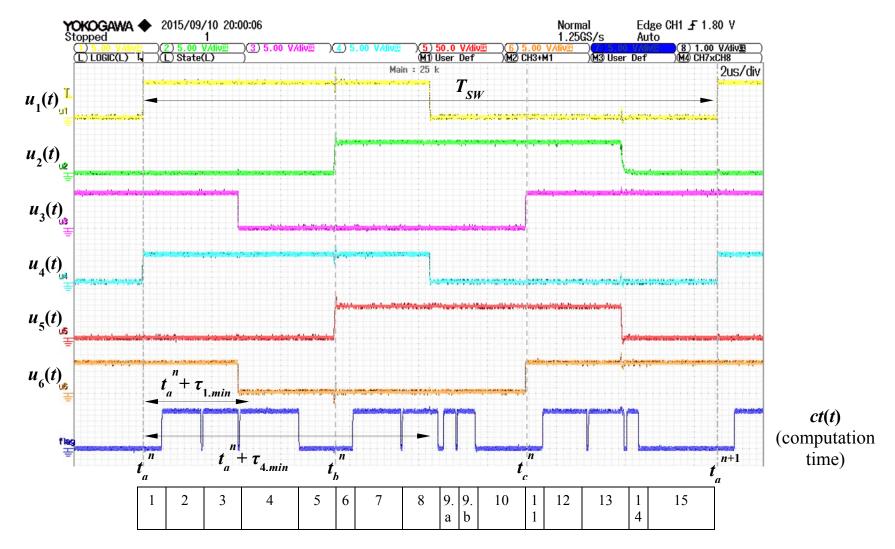

| Fig. 4 | .13. Execution sequence.                                                                                                                              | 80 |

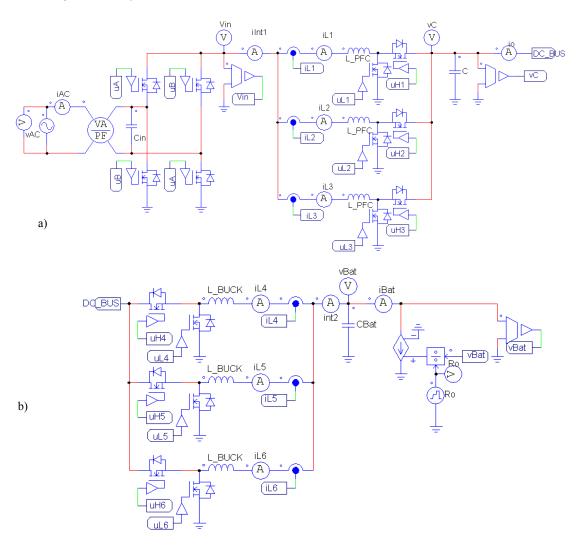

| •      | 3.1. PSIM model of the battery charger. a) Grid synchronised rectifier and PFC stage. b) BCR stage and emulated battery as a variable $R_o$ .         | 84 |

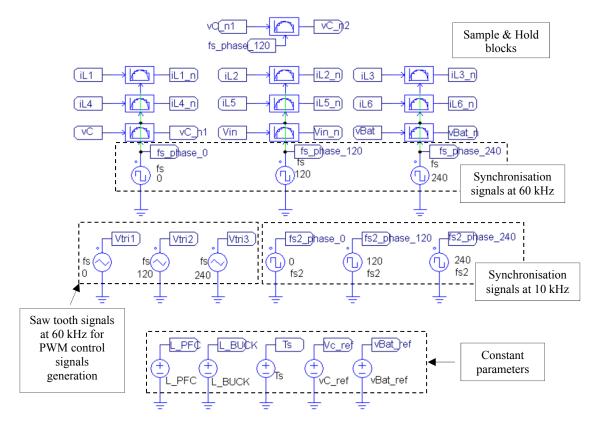

| _      | 5.2. Synchronisation signals, sample & hold blocks for ADC emulation, triangular waveforms for PWM control signals generation and constant parameters | 85 |

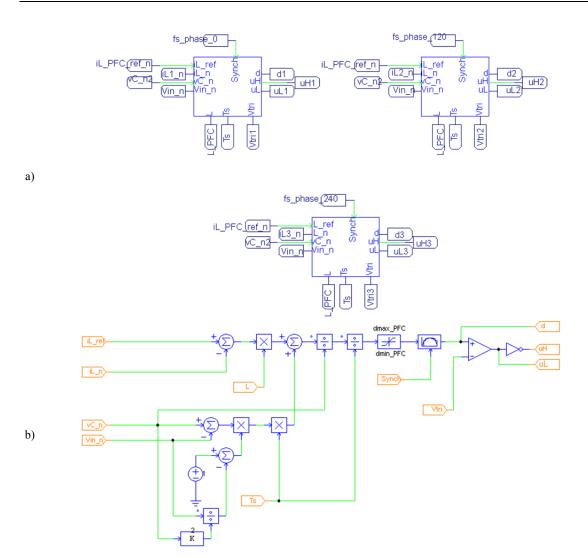

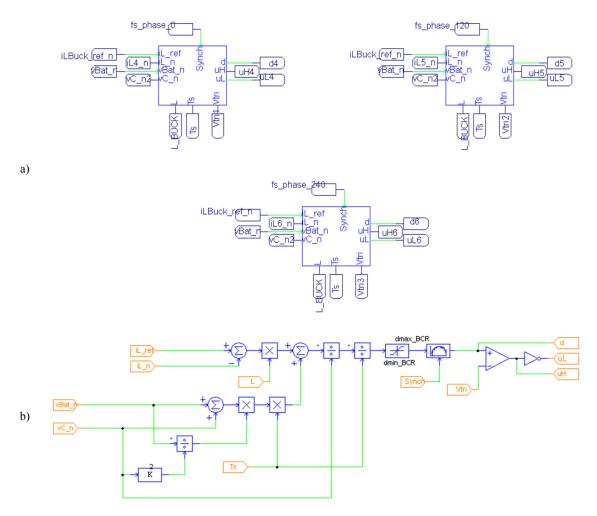

| •      | 5.3. a) Submodules of the three PFC inductor current controllers. b) Content of the submodules.                                                       | 86 |

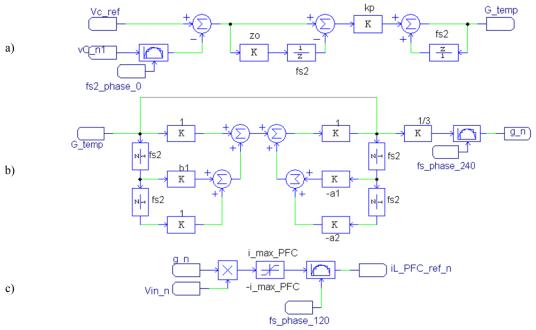

| •      | (.4. a) PI DC-link voltage controller. b) Notch filter. c) PFC inductor current reference calculation.                                                | 86 |

| -      | 5.5. a) Submodules of the three inductor current controllers for the BCR stage. b) Content of the submodules.                                         | 87 |

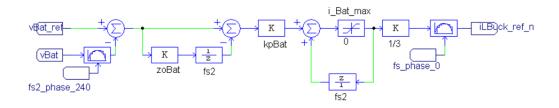

| Fig. 5 | .6. PI battery voltage controller.                                                                                                                    | 87 |

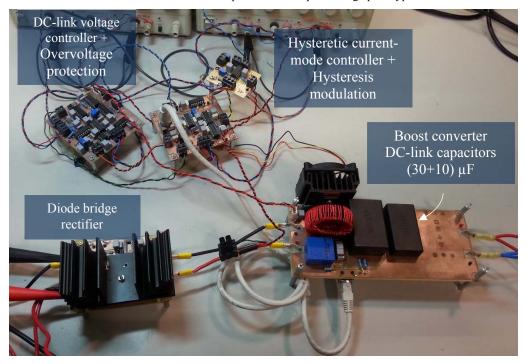

|        | 7.7. Experimental set-up for testing of the implemented prototype. a) General view. b)                                                                | 88 |

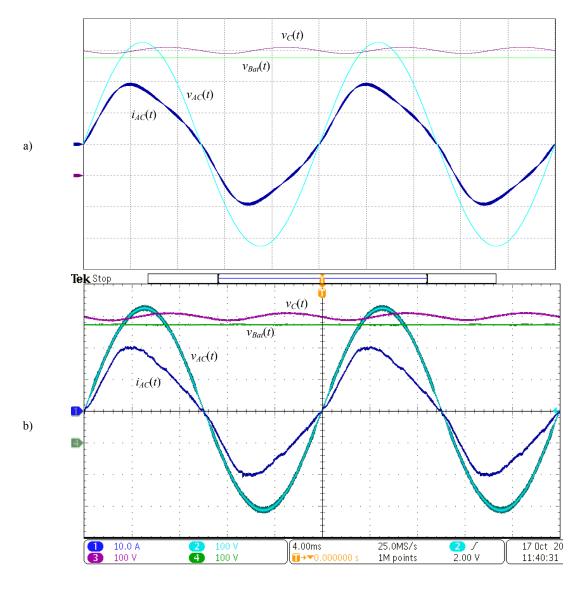

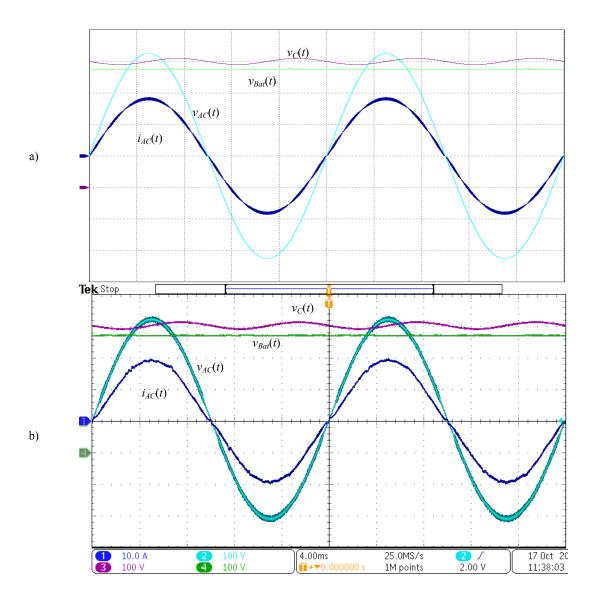

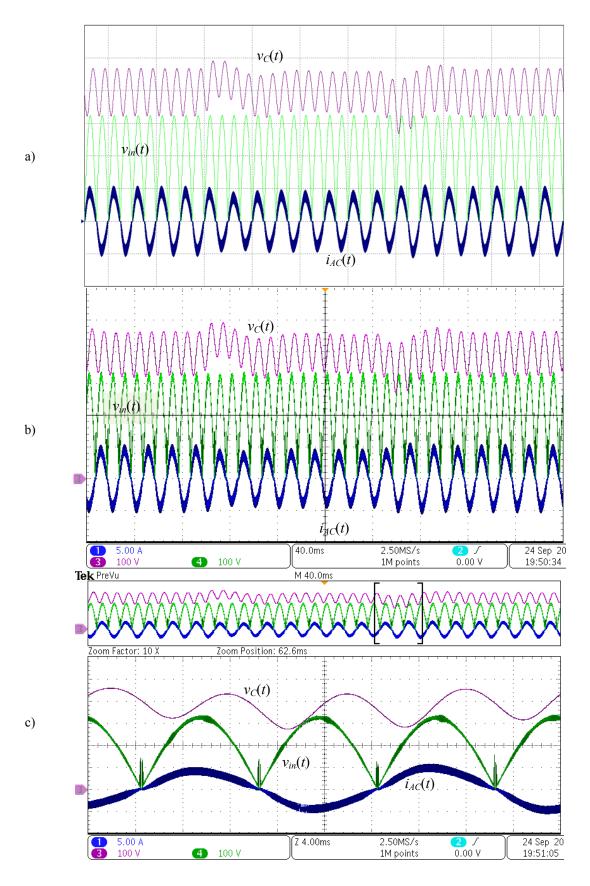

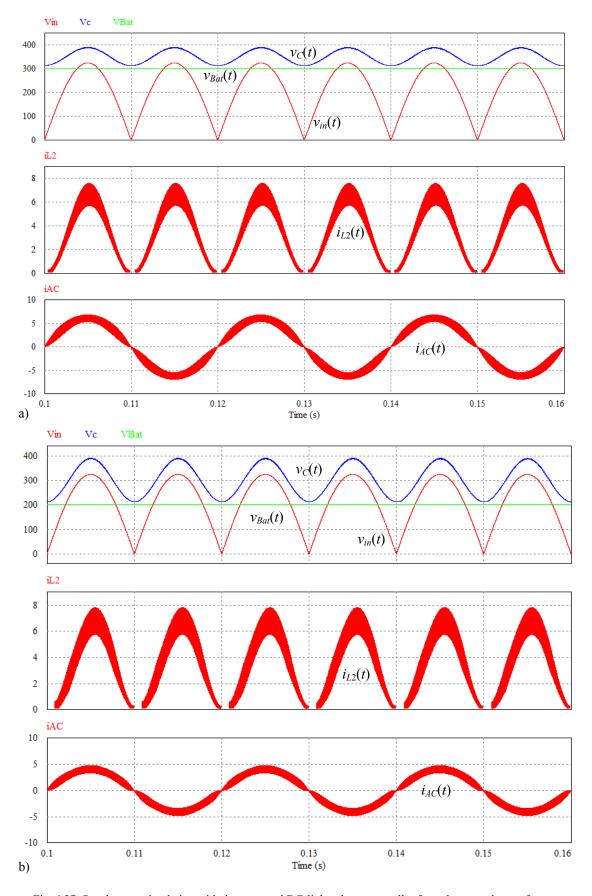

| Fig. | 5.8. Steady-state operation of the battery charger under maximum load conditions and without using the Notch filter (4 ms/div). CH1: line current $i_{AC}(t)$ (10 A/div). CH2: line voltage $v_{AC}(t)$ (100 V/div). CH3: DC-link voltage $v_{C}(t)$ (100 V/div). CH4: battery voltage $v_{Bat}$ (100 V/div). a) Simulation. b) Experimental result. | . 90 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

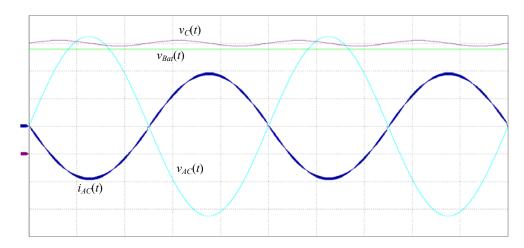

| Fig. | 5.9. Steady-state operation of the battery charger under maximum load conditions and using the Notch filter (4 ms/div). CH1: $i_{AC}(t)$ (10 A/div). CH2: $v_{AC}(t)$ (100 V/div). CH3: $v_{C}(t)$ (100 V/div). CH4: $v_{Bat}$ (100 V/div). a) Simulation. b) Experimental result                                                                    | . 91 |

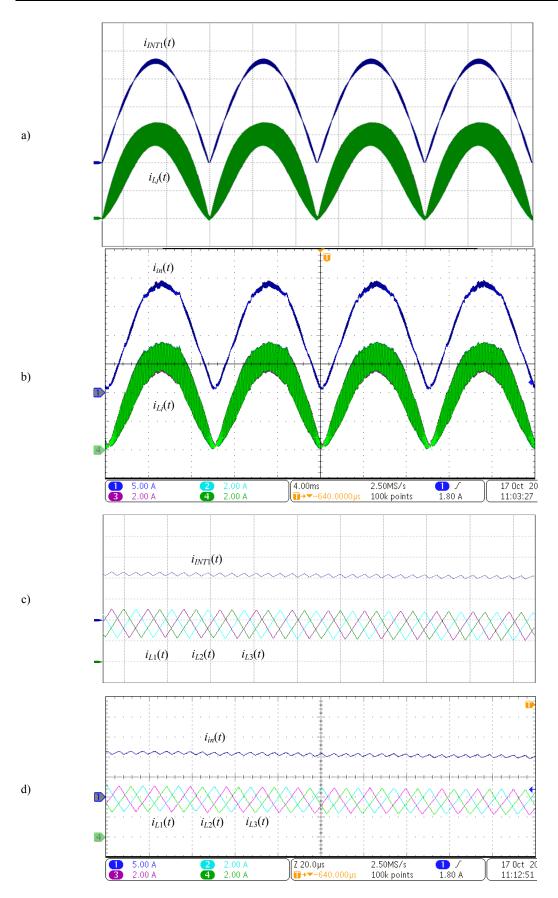

| Fig. | 5.10. Currents from the PFC stage. CH1: $i_{INT1}(t)$ (5 A/div). CH2: $i_{L1}(t)$ (2 A/div). CH3: $i_{L2}(t)$ (2 A/div). CH4: $i_{L3}$ (2 A/div). a) Simulation, b) experimental result (4 ms/div). Zoom c) simulation, d) experimental result (20 $\mu$ s/div).                                                                                     | . 92 |

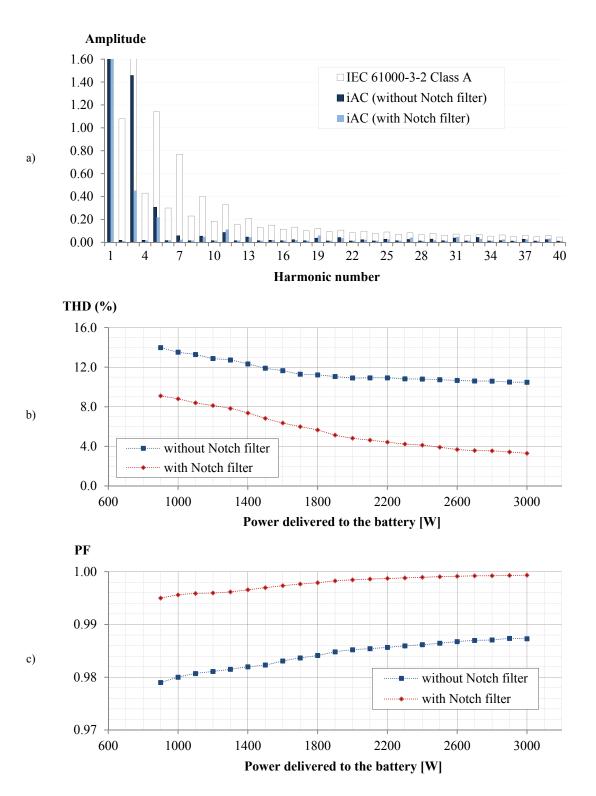

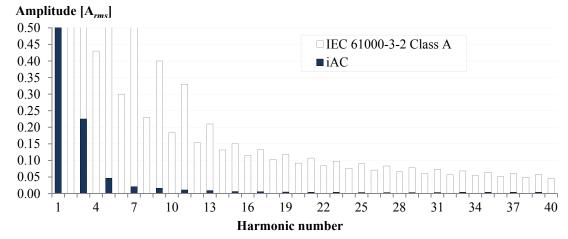

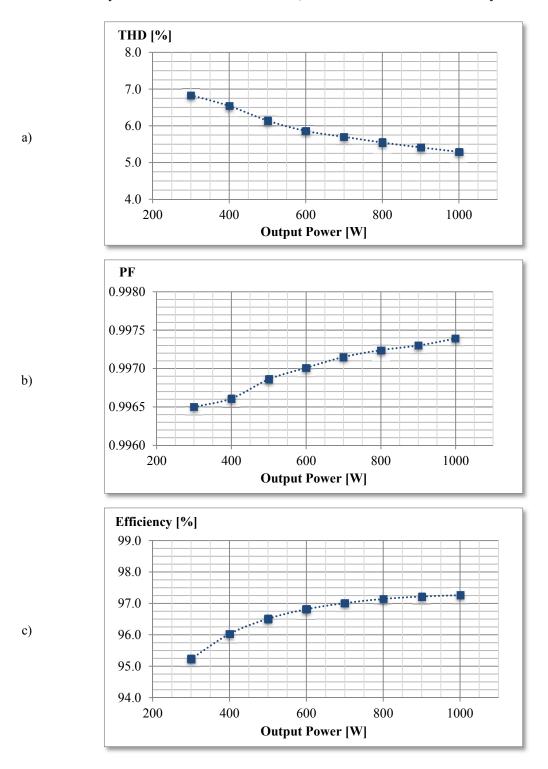

| Fig. | 5.11. Measured a) low-frequency harmonic spectrum of line current $i_{AC}(t)$ under maximum load conditions, b) total harmonic distortion (THD), c) power factor (PF)                                                                                                                                                                                | . 93 |

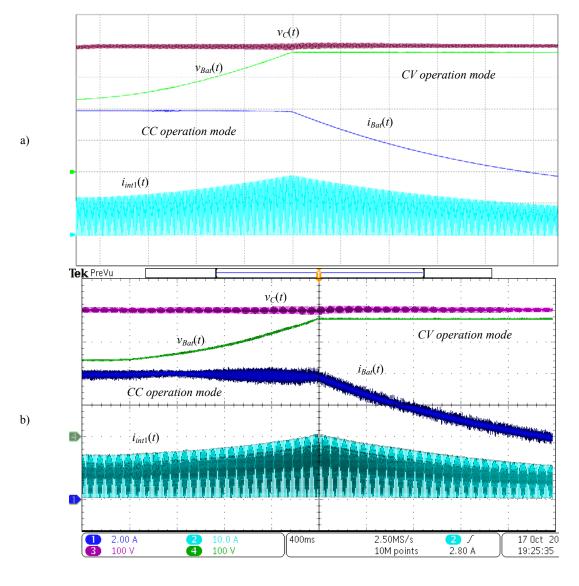

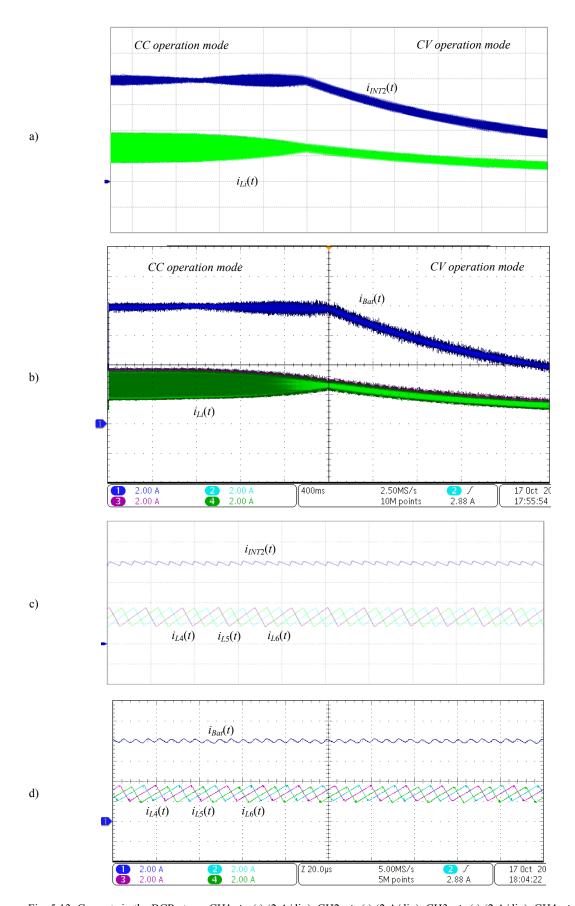

| Fig. | 5.12. Battery charging emulation with CC-CV operation mode transition (400 ms/div). CH1: $i_{Bat}(t)$ (2 A/div). CH2: $i_{int1}(t)$ (10 A/div). CH3: $v_C(t)$ (100 V/div). CH4: $v_{Bat}$ (100 V/div). a) Simulation. b) Experimental result.                                                                                                        | . 94 |

| Fig. | 5.13. Currents in the BCR stage. CH1: $i_{Bat}(t)$ (2 A/div). CH2: $i_{L4}(t)$ (2 A/div). CH3: $i_{L5}(t)$ (2 A/div). CH4: $i_{L6}$ (2 A/div). a) Simulation, b) experimental result (400 ms/div). Zoom c) simulation, d) experimental result (20 $\mu$ s/div)                                                                                       | . 96 |

| Fig. | 5.14. Simulation result of the steady-state operation of the battery charger under maximum load conditions for Vehicle-to-Grid operation (4 ms/div). CH1: $i_{AC}(t)$ (10 A/div). CH2: $v_{AC}(t)$ (100 V/div). CH3: $v_{C}(t)$ (100 V/div). CH4: $v_{Bat}$ (100 V/div)                                                                              | . 97 |

| Fig. | 6.1. General block diagram of a single-phase power supply system based on two cascaded stages and a DC-link capacitor.                                                                                                                                                                                                                               | 100  |

| Fig. | 6.2. PFC stage based on a boost converter and a diode bridge.                                                                                                                                                                                                                                                                                        | 100  |

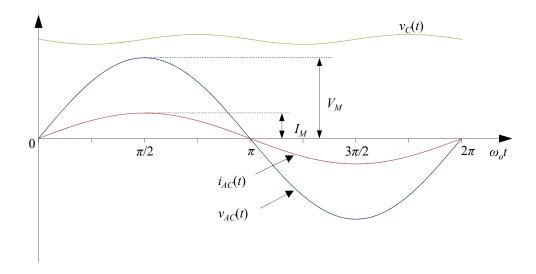

| Fig. | 6.3. Line voltage $v_{AC}(t)$ , line current $i_{AC}(t)$ and DC-link capacitor voltage $v_C(t)$                                                                                                                                                                                                                                                      | 102  |

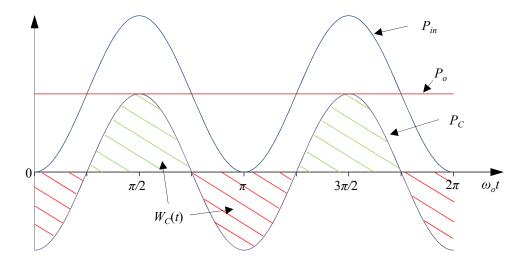

| Fig. | 6.4. Absorbed input power $P_{in}$ , delivered output power $P_o$ , capacitor power $P_C$ and capacitor energy $W_C(t)$ .                                                                                                                                                                                                                            | 102  |

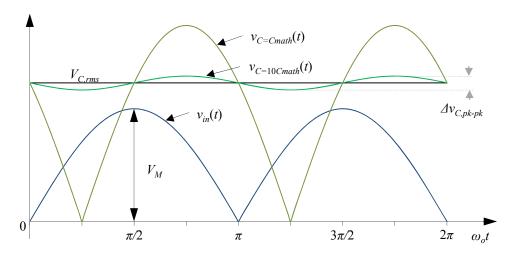

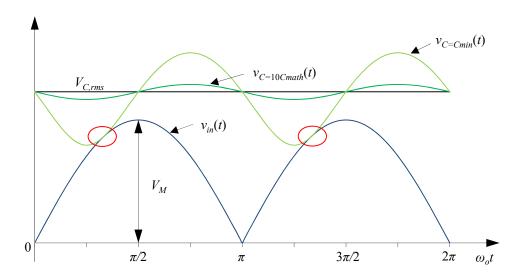

| Fig. | 6.5. Theoretical DC-link voltage waveforms for $C=C_{math}$ , $C=10C_{math}$ and rectified input voltage $v_{in}(t)$ .                                                                                                                                                                                                                               | 103  |

| Fig. | 6.6. Conventional PFC control design for single-phase applications based on two cascaded stages. Second stage is modelled as a CPL.                                                                                                        | 105 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. | 6.7. Theoretic DC-link voltage waveforms for C=10 $C_{math}$ , C= $C_{min}$ and rectified input voltage $v_{in}(t)$ .                                                                                                                      | 106 |

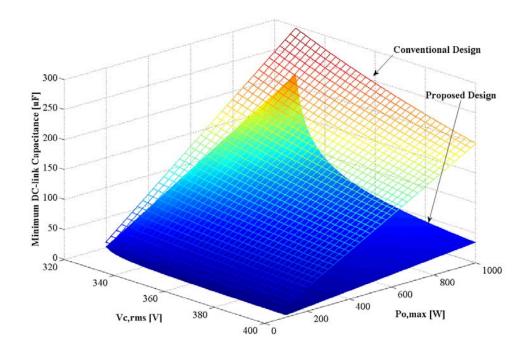

| Fig. | 6.8. DC-link capacitance according to a conventional design ( $\Delta v_{C,pk-pk}=10\%$ ) and the proposed design as a function of voltage $V_{C,RMS}$ and output power $P_{o,max}$ for $V_{AC}=230$ $V_{RMS}$ and $f_{AC}=50$ Hz.         | 108 |

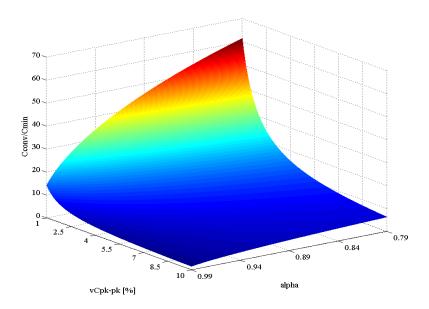

| Fig. | 6.9. $C_{conv}/C_{min}$ relation depending on $\Delta v_{C,pk-pk}(\%)$ and $\alpha$ .                                                                                                                                                      | 109 |

| Fig. | $6.10.\ V_{C,RMS}$ adjustment depending on the load conditions considering the finally selected DC-link capacitance.                                                                                                                       | 109 |

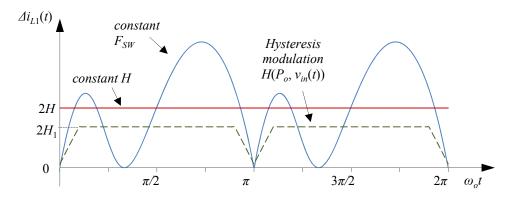

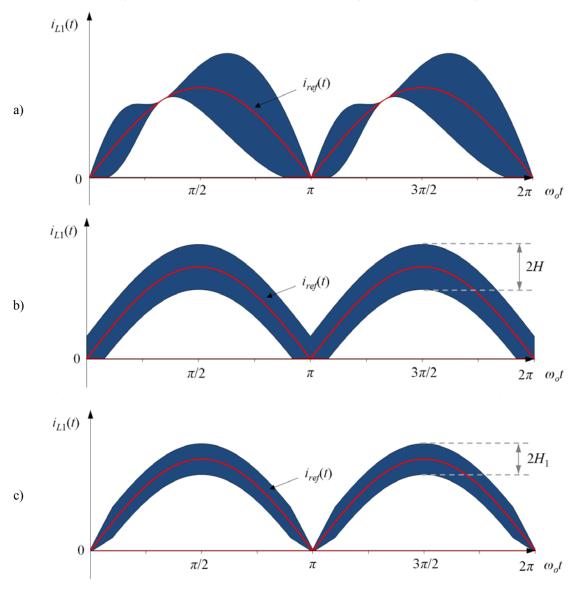

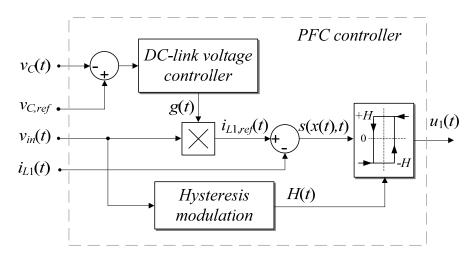

| Fig. | 6.11. Inductor current ripple depending on the applied control technique: constant switching frequency-based controller, hysteretic current-mode controller with constant hysteresis or modulated hysteresis.                              | 111 |

| Fig. | 6.12. Theoretic inductor current under different current-mode control techniques. a) Constant switching frequency-based controller. b) Constant hysteresis-based controller. c) Modulated hysteresis-based controller.                     | 111 |

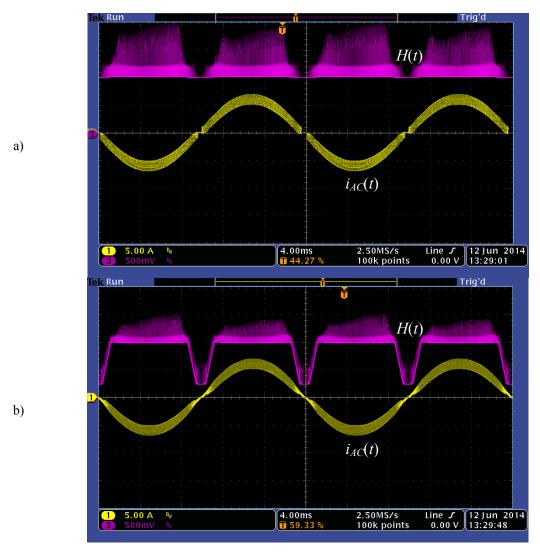

| Fig. | 6.13. Line current under hysteretic current-mode control with a) constant hysteresis, b) modulated hysteresis. CH1: line current $i_{AC}(t)$ (5 A/div), CH3: hysteresis signal $H(t)$ (500 mV/div).                                        | 112 |

| Fig. | 6.14. Block diagram of the proposed PFC controller.                                                                                                                                                                                        | 113 |

| Fig. | 6.15. Conduction topologies of a boost converter. a) ON-state. b) OFF-state                                                                                                                                                                | 114 |

| Fig. | 6.16. Small-signal representation of the PFC stage.                                                                                                                                                                                        | 117 |

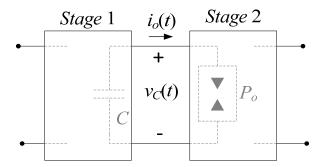

| Fig. | 6.17. System model based on two cascaded stages.                                                                                                                                                                                           | 118 |

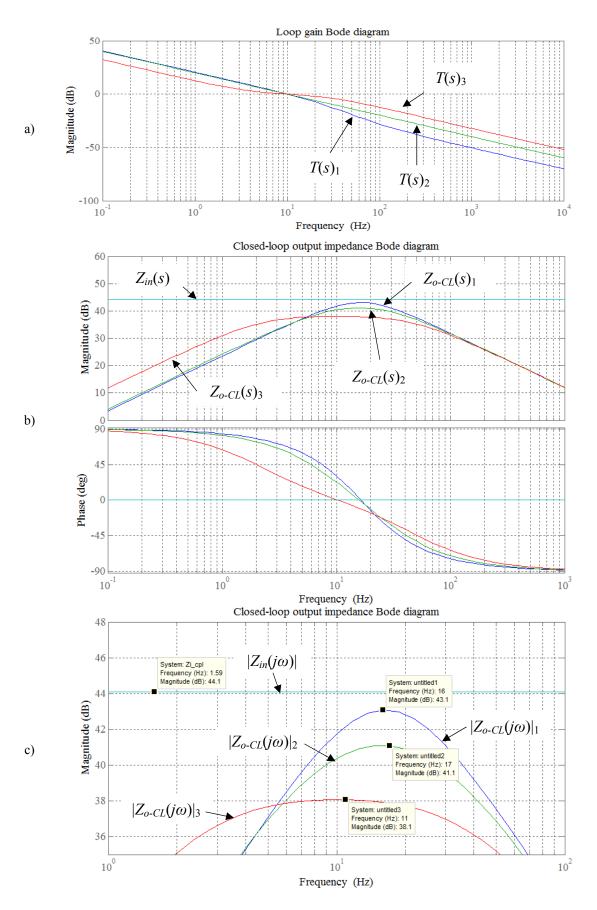

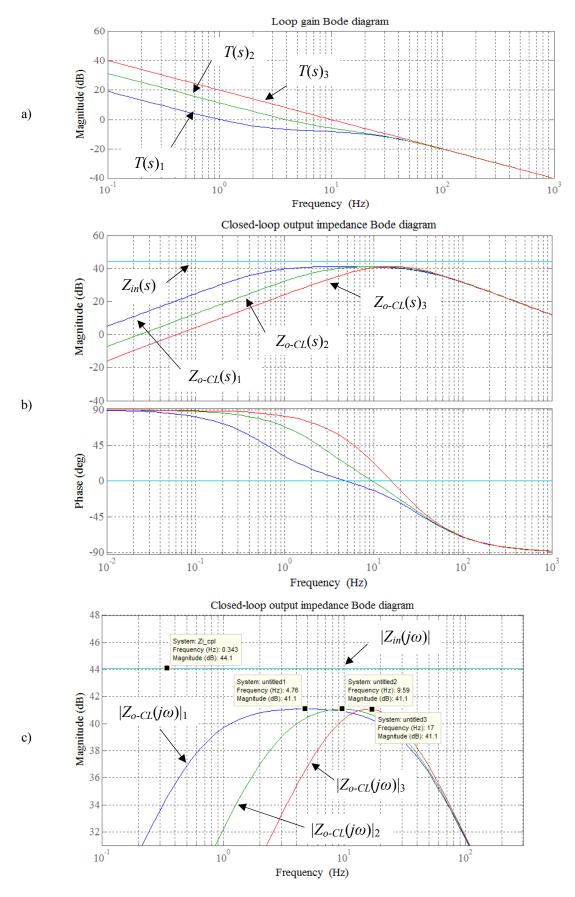

| Fig. | 6.18. Bode diagram of a) loop gain, b) closed-loop output impedance $Z_{o\text{-}CL,1\text{st}}(s)$ and $Z_{in}(s)$ , c) detail of the maximum magnitudes. Sub-indexes 1, 2 and 3 stands for $\Delta Z_{dif}$ 1 dB, 3 dB and 6 dB designs. | 124 |

| Fig. | 6.19. Bode diagram of a) loop gain, b) closed-loop output impedance $Z_{o\text{-}CL,1\text{st}}(s)$ and $Z_{in}(s)$ , c) detail of the maximum magnitudes. Sub-indexes 1, 2 and 3 stands for $f_C$ 1 Hz, 4 Hz and 10 Hz respectively       | 125 |

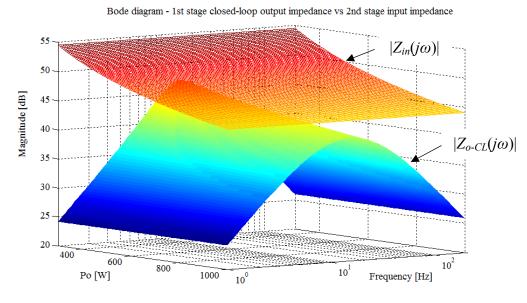

| Fig. | 6.20. Middlebrook's stability criterion verification of the proposed controller for the                                                                                                                                                                                                                                            |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | load range 300 W – 1 kW                                                                                                                                                                                                                                                                                                            | 126 |

| Fig. | 6.21. Sensing circuitry of power signals.                                                                                                                                                                                                                                                                                          | 127 |

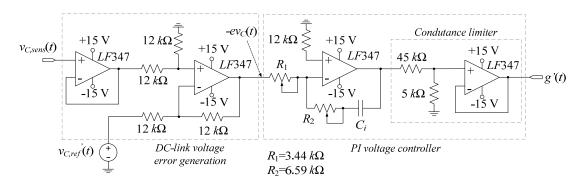

| Fig. | 6.22. DC-link voltage controller.                                                                                                                                                                                                                                                                                                  | 127 |

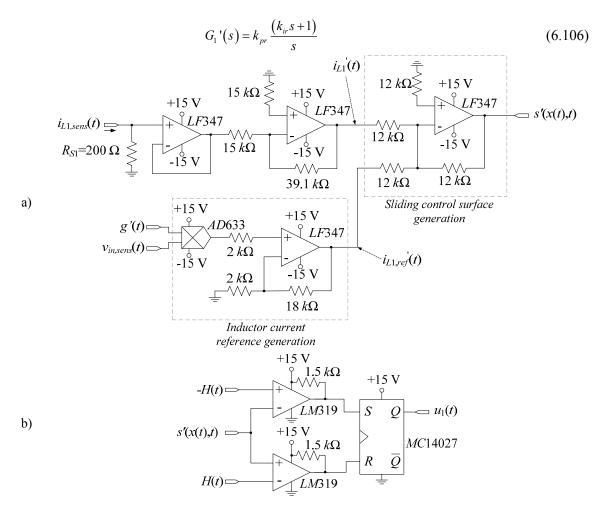

| Fig. | 6.23. Hysteretic current-mode controller. a) Sliding-mode control surface implementation. b) Control signal generation.                                                                                                                                                                                                            | 128 |

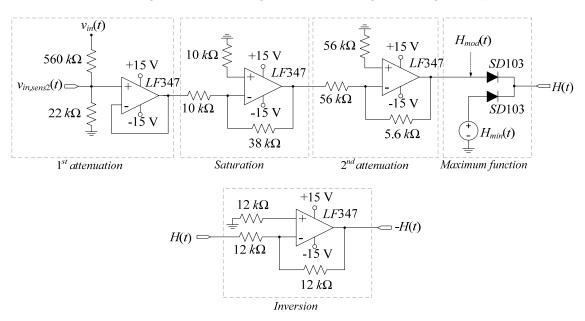

| Fig. | 6.24. Employed circuit for hysteresis modulation.                                                                                                                                                                                                                                                                                  | 129 |

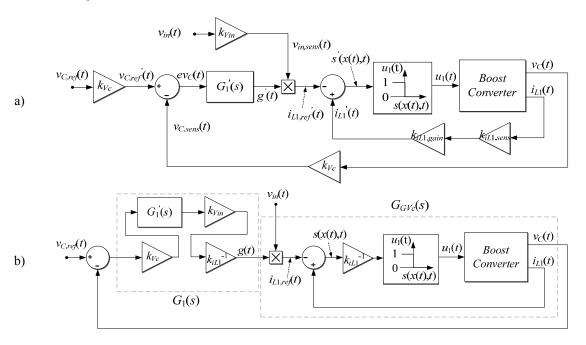

| Fig. | 6.25. Block diagram of the analogue circuit. a) Implemented circuit. b) Equivalent diagram.                                                                                                                                                                                                                                        | 130 |

| Fig. | 6.26. Implemented power converter and analogue controller                                                                                                                                                                                                                                                                          | 131 |

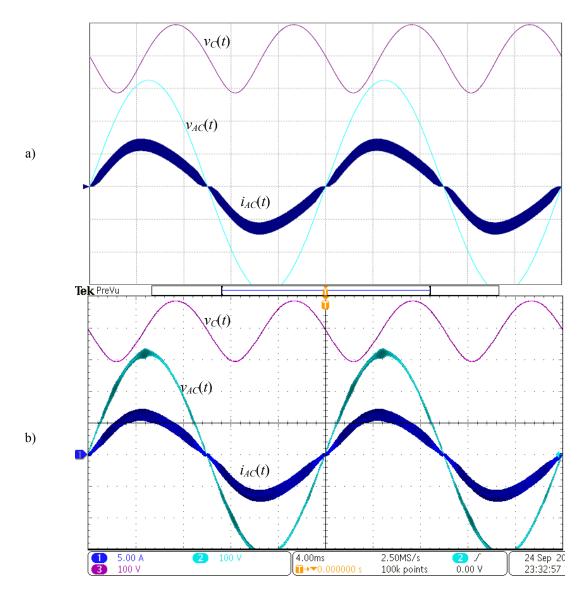

| Fig. | 6.27. Steady-state response of the pre-regulator (4 ms/div): a) simulation and b) experimental results. CH1: line current $i_{AC}(t)$ (5 A/div). CH2: line voltage $v_{AC}(t)$ (100 V/div). CH3: DC-link capacitor voltage $v_C(t)$ (100 V/div).                                                                                   | 132 |

| Fig. | 6.28. IEC 61000-3-2 Class A harmonic limits and measured low-frequency harmonics of line current $i_{AC}(t)$ under nominal power test conditions.                                                                                                                                                                                  | 132 |

| Fig. | 6.29. Measured a) total harmonic distortion (THD), b) power factor (PF) and c) efficiency.                                                                                                                                                                                                                                         | 133 |

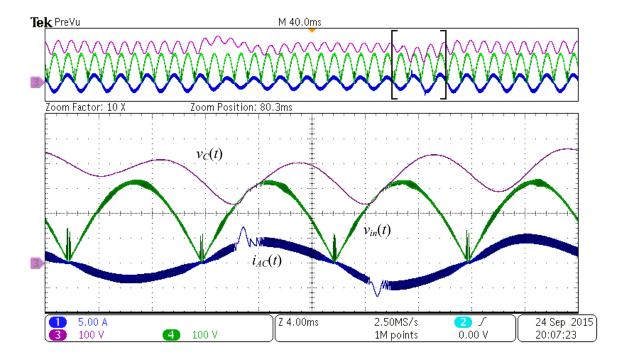

| Fig. | 6.30. Transient response of the pre-regulator to periodic step output load perturbations of 100 W (100 ms/div): a) simulation and b) experimental results. c) Zoom of transient response to a load step change from 600 W to 700 W (4 ms/div). CH1: $i_{AC}(t)$ (5 A/div). CH3: $v_C(t)$ (100 V/div). CH4: $v_{in}(t)$ (100 V/div) | 134 |

| Fig. | 6.31. Line current distortion for transient responses from 550 W to 700 W (4 ms/div). CH1: $i_{AC}(t)$ (5 A/div). CH3: $v_C(t)$ (100 V/div). CH4: $v_{in}(t)$ (100 V/div)                                                                                                                                                          | 135 |

| Fig. | 6.32. Proposed control design for a two-stage based battery charger with very low DC-link capacitance and DC-link voltage regulation from the second stage.                                                                                                                                                                        | 136 |

| Fig. | 6.33. First stage is modelled as an LFR. A buck converter is employed to configure the second stage.                                                                                                                                                                                                                               | 136 |

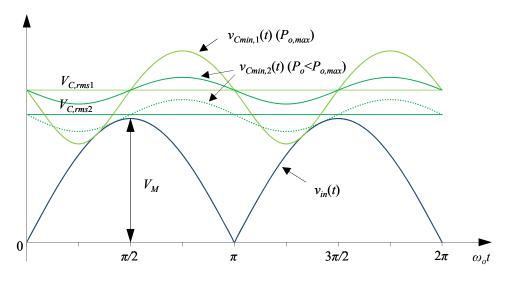

| Fig. | 6.34. Proposed DC-link voltage waveform.                                                                                                                                                                                                                                                                                           | 137 |

| Fig. | 6.35. Conduction topologies of a buck converter. a) ON-state. b) OFF-state                                                                                                                                                                                                                                                         | 138 |

| Fig. | 6.36. Gain loop frequency response.                                                          | 140 |

|------|----------------------------------------------------------------------------------------------|-----|

| Fig. | 6.37. Steady-state simulation with the proposed DC-link voltage controller from the          |     |

|      | second stage for two different battery voltage conditions. a) Simulation A $V_{Bat}$ =300 V. |     |

|      | b) Simulation B $V_{Bat}$ =200 V.                                                            | 141 |

| Fig. | 7.1. Enhanced PFC controller for low DC-link capacitance conditions.                         | 147 |

| Fig. | 7.2. Unidirectional 1 kW battery charger prototype with low DC-link capacitance and          |     |

|      | FPGA-based control board.                                                                    | 147 |

## List of tables

| Table 2.1. Design specifications.                                                                                                     | 19  |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1. Discrete-time system modelling equations.                                                                                  | 53  |

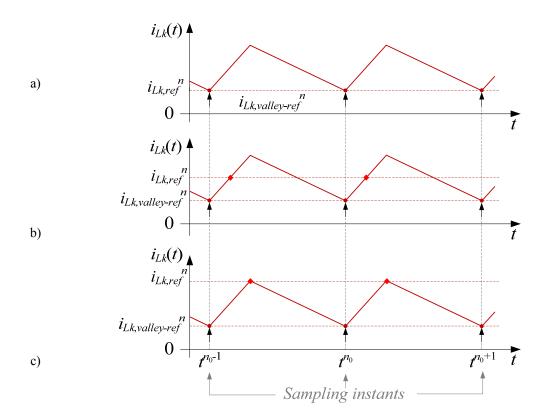

| Table 4.1. Definition of the inductor current valley reference value depending on the desired type of current-mode control technique. | 60  |

| Table 4.2. Equivalent control $\tau_{eq,k}^n$ for boost and buck converters and different types of current-mode control techniques.   | 62  |

| Table 4.3. Small-signal perturbation signals to DC-link voltage transfer functions.                                                   | 72  |

| Table 4.4. Design parameters for the DC-link voltage controller.                                                                      | 74  |

| Table 4.5. Parameter values of the DC-link voltage regulation loop.                                                                   | 74  |

| Table 4.6. Design parameters for the battery voltage controller.                                                                      | 77  |

| Table 4.7. Minimum duty cycles in each stage under steady-state operation conditions                                                  | 79  |

| Table 6.1. Parameters for a DC-link capacitor conventional design.                                                                    | 105 |

| Table 6.2. Parameters for the first DC-link capacitance reduction approach                                                            | 107 |

| Table 6.3. Power stage parameter values.                                                                                              | 122 |

| Table 6.4. Design of three different DC-link voltage controllers with the same cut-off frequency.                                     | 123 |

| Table 6.5. Design of three different DC-link voltage controllers with the same $\Delta Z_{dif}$                                       | 126 |

| Table 6.6. Selected components for the power stage prototype.                                                                         | 131 |

| Table 6.7. Nominal power conditions.                                                                                                  | 131 |

| Table 6.8. Design parameters for the DC-link voltage controller with highly reduced capacitance.                                      | 139 |

| Table 6.9. Simulation parameters for the second DC-link capacitance reduction approach                                                | 142 |

### List of abbreviations, symbols and variables

#### **Abbreviations**

AC Alternating current

ADC Analogue-to-digital converter BCR Battery current regulation BMS Battery management system

CC Constant current

CCM Continuous conduction mode

CPL Constant power load

CPS Constant power source

CV Constant voltage

DB Diode bridge

DC Direct current

DPWM Digital pulse width modulation

DSC Digital signal controller

EMI Electromagnetic interference

EV Electric vehicle

EVSE Electric vehicle supply equipment

G2V Grid-to-vehicle

GPIO General purpose input output

HEV Hybrid electric vehicle

ICE Internal combustion engine

IEC International Electrotechnical Commission

LFR Loss-free resistor Li-ion Lithium-ion

MOSFET Metal-oxide-semiconductor field-effect transistor

NiMH Nickel-metal hydride OA Operational amplifier

PF Power factor

PFC Power factor correction

PHEV Plug-in hybrid electric vehicle

PI Proportional-integral

POPI Power output power input

PWM Pulse width modulation

SAE Society Automotive Engineers

SG Smart grid Si Silicon

SiC Silicon carbide

SM Sliding-mode

SMC Sliding-mode control

SoC State of charge

THD Total harmonic distortion

V2G Vehicle-to-grid

#### Symbols and variables

α Ratio between peak-line voltage and RMS DC-link voltage

A Ampere, current unit  $\Delta$  Increment or ripple

$\Delta i_{L, pk-pk}$  Peak-to-peak inductor current ripple

$\Delta v_{Bat, pk-pk}$  Peak-to-peak ripple of the battery voltage

$\Delta v_{C, pk-pk}$  Peak-to-peak ripple of the DC-link capacitor voltage

$\Delta Z_{dif}$  Magnitude difference in dBs

Capacitor (also used as a subscript)

$C_{Bat}$  Battery capacitor  $C_{in}$  Input capacitor cos Cosine operation d Duty-cycle D Diode

F Farad, capacitance unit  $f_{AC}$  Line frequency  $f_C$  Cut-off frequency

$fs_2$  DC-link regulation loop frequency execution rate

$f_{SW}$  Switching frequency

$F_{RHC}$  Ripple harmonic cancellation function

g Emulated input conductance by each PFC stage cell Emulated input conductance by the PFC stage

H Henry, inductance unit

H Hysteresis  $i_{AC}$  Line current  $I_{AC,RMS}$  RMS line current

$I_{AC,RMS max}$  Maximum RMS line current  $i_{Bat}(t)$  Instantaneous battery current Average battery current

$i_{in}(t)$  Instantaneous rectified input current

$I_{in}$  Average input current

$i_{INT}(t)$  Instantaneous current sum of three interleaved inductor currents

$i_L(t)$  Instantaneous inductor current  $I_L$  Average inductor current

$i_o(t)$  Instantaneous output current from the PFC stage  $I_o$  Average output current from the PFC stage

k Constant parameter  $k_i$  Integral parameter  $k_p$  Proportional parameter

L Inductor (also used as a subscript)

*m* Inductor current slopes

M Type of current-mode controller

Average battery power

$P_{cell,max}$  Maximum rated power for one cell

$P_{in}$  Average input power  $P_{o}$  Average output power  $P_{o, max}$  Maximum load conditions

Q MOSFET

$Q_{rr}$  Reverse recovery charge

r Loss-free resistor emulated resistance

R Resistor

RMS Root mean square value (also used as a subscript)

s Sliding-mode control surface

S Siemens  $(\Omega^{-1})$ sin Sine operation

t Time

*τ* ON-state conduction time

T Loop gain

tan Tangent operation

$\tau_{eq}$  ON-state conduction time equivalent control DC-link regulation loop period execution rate

$T_{SW}$  Switching period

u(t) Instantaneous control signal

$u_L(t)$  Instantaneous control signal for low-side controlled switches  $u_H(t)$  Instantaneous control signal for high-side controlled switches

V Volt, voltage unit

$v_{AC}(t)$  Instantaneous line voltage

$V_{AC}$  Line voltage  $V_{AC, RMS}$  RMS line voltage

$v_{Bat}(t)$  Instantaneous battery voltage

$V_{Bat}$  Battery voltage

$v_C(t)$  Instantaneous DC-link capacitor voltage  $V_C$  Average DC-link capacitor voltage  $V_{C, RMS}$  RMS DC-link capacitor voltage  $v_{in}(t)$  Instantaneous rectified input voltage  $V_{in}$  Average rectified input voltage

$V_M$  Peak line voltage Watt, power unit

W Energy

$\omega_C$  Cut-off angular frequency

$\omega_N$  Discrete centre frequency of Notch filter

$\omega_o$  Angular line frequency

Z Impedance  $Z_{in}$  Input impedance

$Z_{o-CL}$  Closed-loop output impedance

x(t) State vector

$\Omega$  Ohm, resistance unit

#### **Subscripts and superscripts**

Bat Battery

CL Closed-loop

conv Conventional

Relative to buck cells

in Input

$\begin{array}{ccc} & & & \text{Relative to boost cells} \\ & & & \text{Any type of cell} \\ & & & \text{Maximum} \\ & & & & \text{Minimum} \\ & & & & \text{Modulated} \end{array}$

$n^{th}$  switching period

o Output  $p_k$  Peak ref Reference sel Selected sel Steady-state

Transpose operation

# **Abstract**

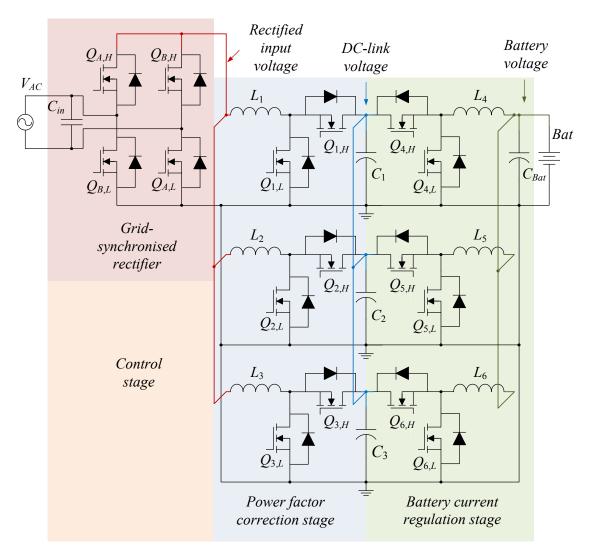

This thesis presents the design and control of a battery charger for plug-in electric vehicles. The aim of this work is to demonstrate that it is possible to apply the discrete-time sliding-mode control theory to design discrete-time inductor current-mode controllers that can operate at a constant switching frequency. This hypothesis is validated in a 3 kW fully digitally controlled bidirectional battery charger that consists of a grid-synchronised rectifier followed by two-cascaded stages. The first stage is based on three interleaved boost converters connected in parallel while the second stage is composed by three interleaved buck converters connected to the battery. The whole digital control has been programmed in a single digital signal controller.

The proposed digital controller has been designed to impose a loss-free resistor behaviour on the first stage aiming to achieve a suitable power factor correction performance. The emulated input resistance of the first stage is adjusted by an outer loop that regulates the DC-link voltage value at  $400~V_{DC}$ . Typical constant current and constant voltage operation modes in battery charging applications are also demonstrated for a battery current of 8 A and battery voltage of 380~V respectively.

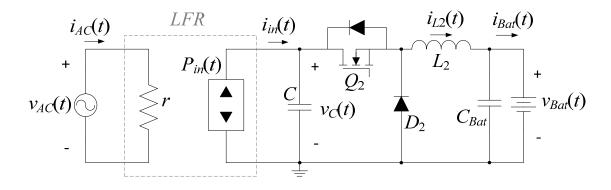

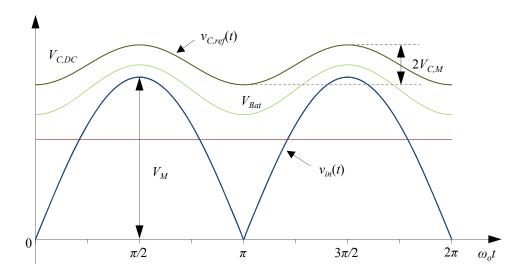

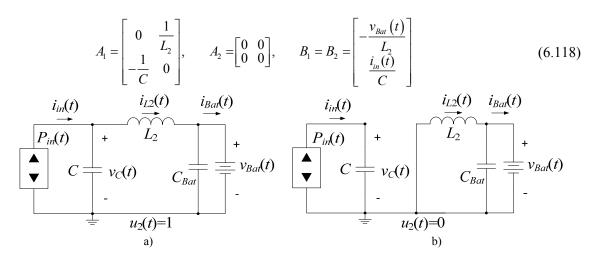

On the other hand, two different DC-link voltage regulation strategies are proposed in this thesis to reduce the DC-link capacitance, which is generally present in many single-phase battery charging applications based on two-cascaded stages. This reduction aims to avoid the use of electrolytic capacitors owing to their low reliability with respect other technologies, such as polypropylene film capacitors. In particular, two different scenarios are analysed in detail. First one considers that the power factor correction stage regulates the DC-link voltage and the second stage behaves as a constant power load. In contrast, the second approach proposes a variable DC-link voltage reference tracking from the second stage, this allowing a further reduction of the DC-link capacitance.

# Chapter 1

## Introduction

Electric vehicles (EVs) have emerged in the recent years as a feasible alternative to internal combustion engine (ICE) vehicles aiming to reduce the high petroleum's dependency and to comply with the more restrictive regulations on emissions that have derived from a major environmental concern about global warming [1, 2]. Despite the fact that the number of EVs is still far from being equal to conventional ICE vehicles, recent advances in energy storage technologies and electronics engineering are boosting their growth in the automotive sector. Although this technology seems to be relatively new, the first EV was invented in 1834 and during the 19<sup>th</sup> century it was produced and commercialised by some American, British and French companies [3, 4]. However, EVs were not considered as a competitive solution to personal road transportation at that time because of the fast advancement of ICE vehicles together with the front barriers associated with the batteries.

Nowadays, some automakers are promoting hybrid electric vehicles (HEV) to tackle the disadvantages of conventional ICE vehicles and pure electric vehicles at once since a fast direct transition to pure electric vehicles is not possible. The architectures of HEVs can be series, parallel, series-parallel or complex [4]. Their control algorithms play an important role because the key point of HEVs is to optimise the driving efficiency through the operation of both ICE and electric motor drive(s) depending on the conditions. Even though these vehicles can generate very low emissions, they cannot be considered completely emissions-free vehicles. Moreover, the need for additional motors, electric storage systems and power converters results in a cost increase of the overall system. According to the adopted terminology, those HEVs that can be charged by being plugged to the grid receive the name of plug-in hybrid electric vehicles (PHEVs).

On the other hand, different companies are betting for full EVs stimulated by the last advancements in energy storage technologies and power electronics. For instance, Tesla Motors has recently presented Model S which is capable to cover a distance of 430 km with a full charge of the battery [5]. However, despite their main advantages, such as high energy efficiency, independence on fossil fuels and zero emissions, the main drawbacks of EVs are their high initial cost, relative short driving autonomy, life cycle of the batteries and slow

#### 1. Introduction

charging. In order to simplify the notation, both PHEVs and pure EVs will be referred as EVs hereinafter.

Regarding the employed battery technology in EVs, the nickel-metal hydride (NiMH) batteries were the most widely used energy storage technology during the 1990s and 2000s due to their high power density and proven safety [6-8]. These days, lithium-ion (Li-ion) batteries are considered the most promising battery technology for EVs as a result of its relatively higher specific energy and power density with respect to lead acid and NiMH. A higher specific energy density is generally traduced into higher autonomy, which is a highly appreciated characteristic in the automotive sector. However, Li-ion batteries need to use a more complex battery management system (BMS) to provide different protections, such as overvoltage, undervoltage, overtemperature and overcurrent; in addition to voltage cell's equalisation [6, 8].

Despite the clear benefits of using EVs, other challenges have still to be faced on the way to electro mobility, such as the lack of charging infrastructure for a deep penetration of EVs in the electric power systems that currently exist. It is clear that EVs represent a new load on the distribution networks and a rapid increase in the number of these vehicles could eventually overload the power grid in case of an unexpected peak of energy consumption [9-12]. This issue gives an excellent opportunity to the concept of smart grids (SGs) to cope with a more efficient management of the electric energy through the distribution networks. In this sense, different approaches have been developed to coordinate the charging of EVs in order to minimise the distribution losses and voltage deviations [13,14]. The implementation of advanced metering infrastructures [9] and safe communication protocols to correctly manage the distribution network and its data is fundamental to make SGs a reality [15, 16].

Furthermore, load shifting has also motivated the research on how EVs connected to the grid can help in load balancing. Unbalanced load conditions between power generation and power consumption are partially generated due to the intrinsic variability of energy generation from renewable energy sources which only produce energy when the primary resource is available. A large number of EVs connected to the grid can be a potential solution to absorb the renewable energy that is not required in the moment that it is being generated [17], hence avoiding its loss [10]. Moreover, the vehicle-to-grid (V2G) capability [18], which enables EVs to inject energy into the grid, can also contribute in stabilizing unbalanced situations during peak hours or even provide electric energy for emergency backup during a power outage [19, 20]. Hence, it can be assured that the bidirectional power flow capability of EVs connected to SGs stands as one key opportunity that electro mobility is offering us to distribute more efficiently both generated and consumed electric energy [21].

#### 1.1 Battery charging modes for EVs

International organizations, such as the International Electrotechnical Commission (IEC) and the Society of Automotive Engineers (SAE), are making an important effort in the development of different standards which regulate the connection of EVs to the power grids. Some of the most important standards are:

- IEC 61851-1 [22]. This standard defines the charging levels and refers to the characteristics and operating conditions of the supply device and the connection to the vehicle.

- IEC 62196-1 [23]. It mainly defines plugs, socket-outlets, vehicle connectors and inlets for EV/PHEVs.

- IEC 61980-1 [24]. It is applied to the equipment for the wireless power transfer from the supply network to electric road vehicles.

- SAE J1772 [25]. It covers the general requirements to facilitate conductive charging of EV/PHEVs in North America.

Four different EV charging modes are defined in [22]. A residual current device is required for all charging modes.

- Mode 1. It is the most basic charging mode. It can be employed in single-phase or three-phase power systems of maximum 250  $V_{RMS}$  and 480  $V_{RMS}$  respectively. The maximum allowed RMS current is 16 A and no specific connector for the EV is required. This mode is not allowed in United States (US).

- Mode 2. It can be employed in single-phase or three-phase power systems of maximum 250  $V_{RMS}$  and 480  $V_{RMS}$  respectively. The maximum allowed RMS current is 32 A and no specific connector for the EV is required. It requires an inline control box.

- Mode 3. The EV is connected to the power grid by means of a specific electric vehicle supply equipment (EVSE) and the inline control box is extended to the employed EVSE. The connection can be single-phase or three-phase and the rated maximum RMS current ranges from 32 A to 250 A.

- Mode 4. The EV is connected to the power grid by means of an off-board battery charger through a DC connection. The maximum rated current is 400 A.

Both modes 1 and 2 are considered slow charging modes and they are expected to take place in residential areas through common household outlets overnight and allow reaching battery full capacity before morning [26]. Charging mode 3 is considered a semi-slow charging mode and, although it can be implemented in most of the environments, it is likely to be installed in

#### 1. Introduction

parking lots, shopping-centres, hotels, etc., for client service [27]. Finally, mode 4 is meant to allow a full recharge of the batteries in few minutes and it is likely to be used in roads and rest areas of highways [26].

#### 1.2 EVs battery chargers

Several battery chargers can be found in the literature and they can be classified according to different criteria [28]. A first classification deals with the battery charger location, which can be inside or outside of the vehicle. Those battery chargers that are placed inside of the vehicle are called *on-board* battery chargers whereas the *off-board* battery chargers are placed outside. On-board battery chargers are more power limited because of their weight and volume constrains, so that they can be used for battery charging modes 1 and 2 [27]. In some cases, on-board battery chargers are integrated with the electric drive of the vehicle in order to avoid adding extra inductors and switches which would only be employed for charging the battery [29-31]. In contrast, off-board battery chargers are mainly designed for battery charging modes 3 and 4 since they are not subjected to weight and size limitations.

Battery chargers can also be classified into conductive and inductive. Conductive battery chargers are defined as those charging systems that use a direct physical contact between the connector and the charge inlet [22]. On the contrary, inductive chargers are those that transfer the power magnetically. Although some works deal with moving chargers [32], inductive chargers are mainly considered for stationary slow charging applications [33].

Another feature that can be used to classify the battery chargers is galvanic isolation. While isolation is recommended for safety reasons, it generally results in heavier and bigger structures which require the use of more complex controllers.

Finally, the bidirectional capability of battery chargers to absorb energy or to inject back to the grid contrasts with unidirectional battery chargers which are only meant to charge the battery. As it can be deduced, bidirectional battery chargers consist in a more expensive, heavier and bigger solution than unidirectional chargers because they generally need extra circuitry to operate in both directions of the power flow.

#### 1.3 EVs battery chargers architectures

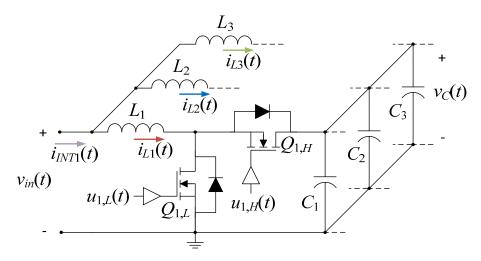

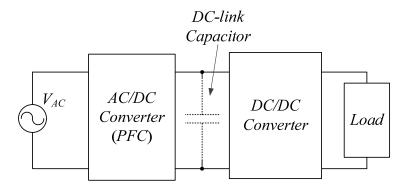

Most of on-board single-phase battery chargers consist of two cascaded stages [28] (see Fig. 1.1). First stage consists of an AC/DC converter that ensures a unity power factor correction (PFC) by absorbing a sinusoidal current from the grid with low current harmonics in order to comply with standard IEC 61000-3-2 [34]. Second stage is based on a DC/DC converter which regulates the current that is delivered to the battery according to its state of charge (SoC) and

matches the difference between the DC-link and battery voltages. Both stages are generally connected by means of a DC-link capacitor. An electromagnetic interference (EMI) filter is connected between the grid and the first stage to comply with standard CISPR 22 [35].

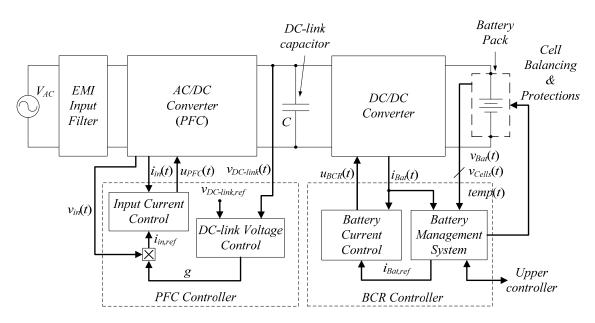

Fig. 1.1. General block diagram of a single-phase on-board battery charger.

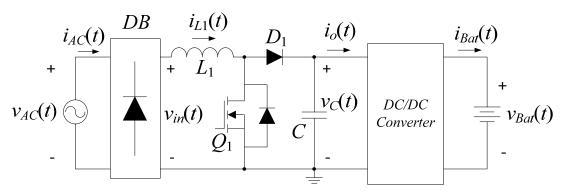

#### 1.3.1 PFC stage circuit topologies

A diode rectifier followed by a boost converter is the most popular unidirectional AC/DC converter owing to its continuous input current, simple structure and grounded transistor [36-38] (see Fig. 1.2.a). However, the main drawback is that an important share of conduction losses is generated by the diode rectifier. For this reason, several bridgeless topologies have been proposed to avoid the use of a rectifier, so that a higher efficiency can be achieved [39-42] (see Fig. 1.2.b-d).

Fig. 1.2. Unidirectional boost-based AC/DC converters. a) Diode rectifier and boost converter. Bridgeless topologies b) Basic topology [39]. c) Totem-pole [40]. d) Dual-boost or semi-bridgeless [41].

#### 1. Introduction

The connection of different converters in parallel is considered a suitable strategy to deal with higher power levels without increasing the current stress of the components (see Fig. 1.3.a). Besides, the interleaving operation of parallel-connected converters was intended to reduce the size of filtering components and the current ripple stress at which input and output capacitors are subjected to [43-45]. This technique can be also extended to bridgeless topologies [46, 47] as can be observed in Fig. 1.3.b-c.

Fig. 1.3. Unidirectional interleaved boost-based AC/DC converters. a) Basic interleaved [43, 44]. b) Totem-pole interleaved [47]. c) Bridgeless interleaved [46].

The diode rectifier of a unidirectional boost converter can be substituted by a synchronous rectifier to allow the bidirectional power flow capability (see Fig. 1.4.a). However, a better efficiency can be achieved if one leg of the synchronous rectifier is replaced by the bidirectional

boost converter (see Fig. 1.4.b). Furthermore, it is also possible to apply the interleaving technique as illustrated in Fig. 1.4.c.

Fig. 1.4. Bidirectional boost-based AC/DC converters. a) Boost converter with synchronous rectifier. b) Full-bridge boost rectifier [48]. c) Full-bridge interleaved [48, 49].

#### 1.3.2 Battery current regulation stage circuit topologies

The voltage of many batteries for EVs ranges from 100 V to 400 V and, for that reason, the most employed DC/DC converter for the battery current regulation (BCR) stage consists of a unidirectional buck converter in order to reduce the voltage from the DC-link to the voltage level of the battery (see Fig. 1.5.a) Sometimes an LC output filter is added to reduce the filtering components (see Fig. 1.5.b). Unidirectional buck-boost converters are also considered due to their capability to step-up and step-down the output voltage (see Fig. 1.5.c). In addition, interleaving technique can be applied on these topologies [50, 51] as depicted in Fig. 1.5.d-e. In particular, a diode rectifier followed by two interleaved buck-boost converters is proposed in [51] to design a single-stage battery charger.

#### 1. Introduction

Fig. 1.5. Unidirectional non-isolated DC/DC converters. a) Buck. b) Buck with output filter. c) Buck-boost. d) Interleaved buck [50]. e) Interleaved buck-boost [51].

Other topologies include a high-frequency switched transformer to provide galvanic isolation between the grid and the battery [27]. In this sense, it is preferable to use high-frequency switched transformers in terms of size and weight than line-frequency transformers [52]. Two of the most widely used topologies are the phase-shifted full-bridge DC/DC converter [53] and the full-bridge series resonant converter [54] (see Fig. 1.6).

Regarding bidirectional topologies, it is very common to find in the literature the use of a two quadrant buck converters (or bidirectional buck converters) since it can be also used for the traction power system to supply energy to the DC-link that feeds the inverters that are used for controlling the electrical drive of the vehicle [55, 56] (see Fig. 1.7.a). Bidirectional topologies for buck-boost [55] and interleaved buck [26, 27, 58] are also proposed in the literature and are depicted in Fig. 1.7.c-d respectively.

Fig. 1.6. Unidirectional isolated DC/DC converters. a) Phase-shifted full-bridge [53]. b) Full-bridge series resonant [54].

Fig. 1.7. Bidirectional non-isolated DC/DC converters. a) Two quadrant buck [55]. b) Two quadrant buck with output filter [59]. c) Buck-boost [55]. d) Interleaved two quadrant buck [58].

#### 1. Introduction

Moreover, dual-active bridge [53, 60], bidirectional full-bridge series resonant [61] converters and derived-topologies are also employed in EV battery charging applications to provide battery chargers with galvanic isolation and bidirectional power flow capability.

Fig. 1.8. Bidirectional isolated DC/DC converters. a) Dual-active bridge [53]. b) Full-bridge series resonant [61].

#### 1.4 Battery charger controllers

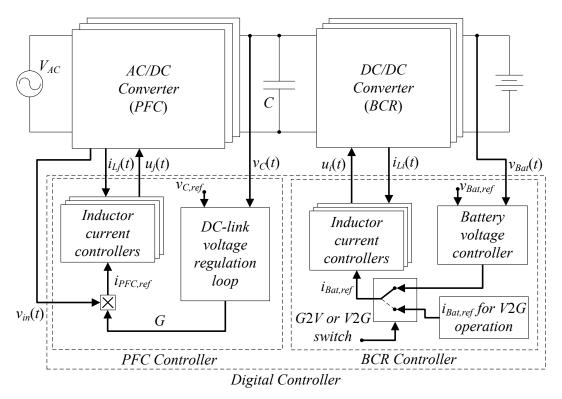

The most common strategy to design the controllers of two-stage-based battery chargers is to design one controller for each stage (see Fig. 1.9). On one hand, the PFC controller ensures the proportionality between the input voltage and the input current, this achieving a unity power factor (PF). In addition, the PFC controller is generally responsible of regulating the DC-link voltage at the specified voltage reference. On the other hand, the BCR stage delivers the required current to the battery depending on its SoC.

The classical strategy for single-phase PFC controllers consists of an inner loop that controls the input current while an outer loop regulates the DC-link voltage [62]. The reference of the inner loop is obtained by multiplying the output of the outer loop with the sensed input voltage. Some approaches use a phase lock loop system to avoid sensing the grid voltage under polluted conditions [63]. The bandwidth of the outer loop has to be sufficiently low (10 Hz - 20 Hz) to reduce the injection of low-frequency harmonics into the grid current. Sometimes, notch filters are introduced into the outer loop to eliminate oscillations at twice the line frequency from the output of DC-link voltage compensator [64], therefore, voltage regulators can be provided with higher bandwidth [65].

Fig. 1.9. Block diagram of a generic battery charger controllers.

Besides, BCR controllers consist of an inner loop that regulates the battery current according to the battery current reference that is generated by the BMS. Battery current reference is calculated depending on the SoC of the battery, which is estimated depending on different parameters such as battery voltage, temperature, etc. The BMS is also responsible of balancing the cells that configure the battery pack as well as activing any protections if necessary. The BMS can be eventually communicated with an upper controller [8].

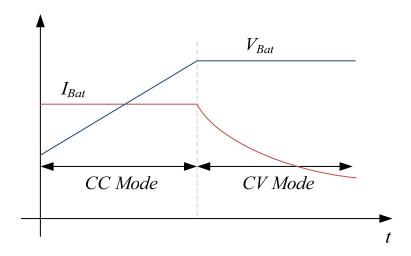

The most popular procedure to charge a battery is the constant current constant voltage method (CC-CV) [66, 67]. The battery is first charged with a constant current (CC) until the battery voltage reaches a predetermined value. In that moment, the operation of the battery charger switches into constant voltage (CV) mode during which the battery current is decreased progressively along with the SoC of the battery (see Fig. 1.10). However, the advancements in microprocessor control units motivated the development of other strategies with higher levels of computational requirements [68]. Some examples are the genetic algorithm in [68] that determines the optimal charging current according to a predictive model of the battery, the fuzzy controller in [69] or the optimal sinusoidal battery current proposed in [70]. The latter approach proposes the frequency and amplitude modulation of a sinusoidal current that is introduced to the battery in order to find the lowest input impedance behaviour of the battery, so that the charging operation is more efficient.

During the last decade, the application of digital controllers has also been extended to the field of power electronics motivated by their cost and size decrease as well as the increase in their computation capability [71]. In the particular case of battery charging applications for EVs, digital controllers are specially preferred instead of analogue controllers due to the high

complexity and cost that would imply the corresponding analogue implementation for the whole system's management. However, the high sampling frequency and the implementation of the control algorithms for the PFC and BCR stages by means of only one digital controller is not obvious. For that reason, some two-stage battery charger manufacturers use two digital controllers or a mixed combination of both analogue and digital controllers to design their solutions [50].

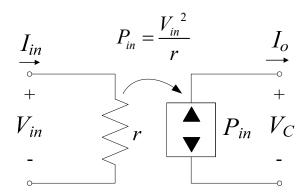

Fig. 1.10. CC-CV battery charging profile.

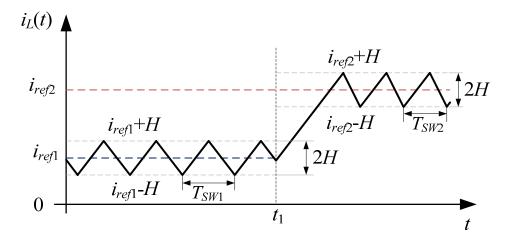

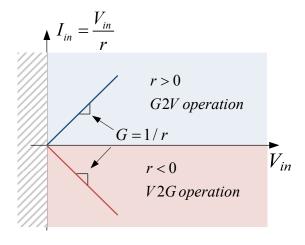

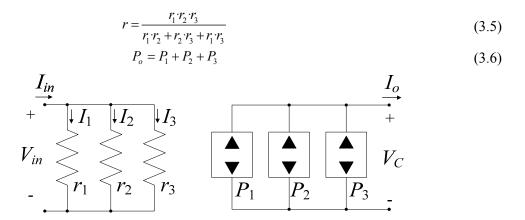

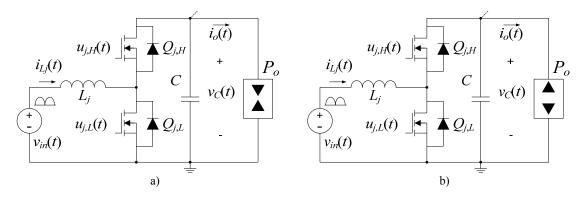

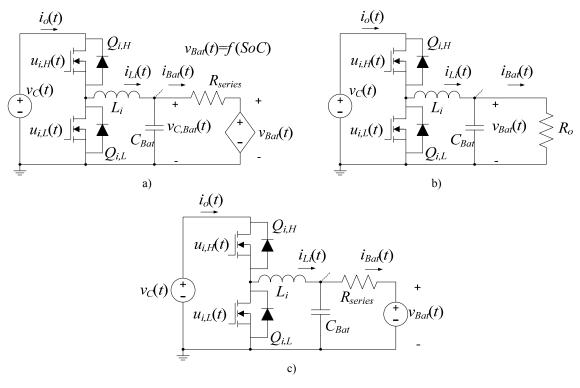

Regarding the design of current-mode controllers, a large number of different inductor currentmode controllers have been proposed in the literature [72, 73] which, roughly speaking, can be classified into two categories, constant and variable switching frequency-based controllers. Hysteretic current-mode control technique is one of the most employed type of variable switching frequency-based current-mode controller and its use goes back in time to the early years of DC-DC switching converters when the resulting regulators were called self-oscillating [74]. This is because the change of topology is produced by the change of the internal state of the converter rather than by the action of an external signal as happens in pulse-width modulation-based (PWM) systems [73]. It has been shown recently that the most appropriate technique to describe the dynamic behaviour of hysteresis-based switching converters is slidingmode control (SMC) approach [75] provided that sliding motions can be induced in the variable structure system describing the switching converter [76]. Moreover, the use of SMC has allowed the synthesis of loss-free resistors (LFRs) [77] by establishing the requirements that power converters must fulfil in order to present a proportional relation between both input voltage and current in sliding regime. An LFR consists in a two-port structure whose input current is proportional to the input voltage and all the absorbed input power  $P_{in}$  is ideally